update

This commit is contained in:

parent

ebeafb1bf9

commit

1b587bbfe8

1

.gitignore

vendored

1

.gitignore

vendored

@ -310,3 +310,4 @@ dist

|

||||

.vscode-test

|

||||

|

||||

citations

|

||||

test.vcd

|

||||

|

||||

53

README.md

53

README.md

@ -91,18 +91,24 @@

|

||||

#### ADC性能指标

|

||||

|

||||

- 面积

|

||||

|

||||

- 功耗

|

||||

|

||||

- 动态范围

|

||||

|

||||

- dBFS

|

||||

|

||||

- THD

|

||||

|

||||

- THD/N

|

||||

|

||||

- SNR

|

||||

|

||||

- DAC SETTLING TIME

|

||||

|

||||

- Glitch impulse area

|

||||

|

||||

|

||||

|

||||

|

||||

|

||||

|

||||

#### ADC误差分析

|

||||

|

||||

@ -180,19 +186,48 @@

|

||||

|

||||

|

||||

|

||||

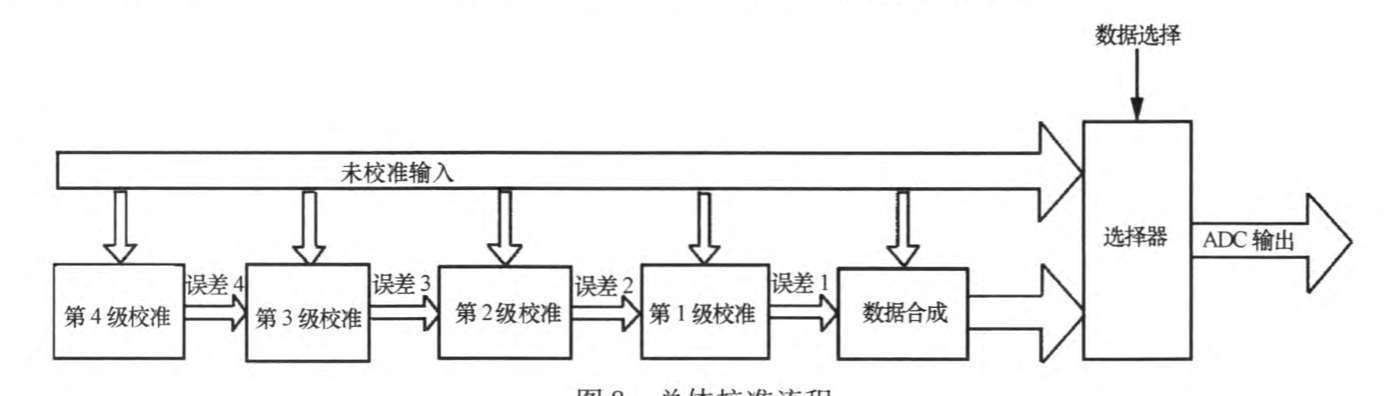

采用有 限状态机的方法一。1刨计算每级校准误差,将每级的校 准信息存入寄存器中。误差运算结束后,将校准参数 对输出码进行校准运算,得到校准后的数字码输出。此数字校准算法可校准对ADC线性影响最大的电容失配误差,适合于1.5 bit级电路和多bit级电 路。明显提高了流水线ADC的无杂散动态范围和有 效精度,对模拟电路的改动较小。

|

||||

采用有 限状态机的方法一。1刨计算每级校准误差,将每级的校 准信息存入寄存器中。误差运算结束后,将校准参数 对输出码进行校准运算,得到校准后的数字码输出。此数字校准算法可校准对ADC线性影响最大的电容失配误差,适合于1.5 bit级电路和多bit级电 路。明显提高了流水线ADC的无杂散动态范围和有效精度,对模拟电路的改动较小。

|

||||

|

||||

- LMS

|

||||

|

||||

|

||||

|

||||

- 迭代法

|

||||

|

||||

|

||||

|

||||

### 开题 答辩稿

|

||||

|

||||

|

||||

|

||||

1. 各位老师好,我是jll,今天我研究的方向是针对ADC的片上数字校准系统。

|

||||

|

||||

|

||||

|

||||

```

|

||||

Σ-Δ ADC 也可以看作是一个同步电压-频率转换器,后跟一个计数器。如果在足够数量的样本中对输出数据流中“1”的数量进行计数,则计数器输出将表示输入的数字值。

|

||||

```

|

||||

|

||||

```

|

||||

调制器中的积分器表示为模拟低通滤波器,其传递函数等于 H(f) = 1/f。该传递函数具有与输入频率成反比的幅度响应。 1 位量化器生成量化噪声 Q,将其注入输出求和块。如果我们让输入信号为 X,输出 Y,那么从输入加法器出来的信号必须是 X – Y。这乘以滤波器传递函数 1/f,结果进入输出夏天。通过检查,我们可以将输出电压 Y 的表达式写为:

|

||||

请注意,随着频率 f 接近零,输出电压 Y 接近 X 时没有噪声成分。在较高频率下,信号分量的幅度接近零,噪声分量接近 Q。在高频下,输出主要由量化噪声组成。本质上,模拟滤波器对信号有低通作用,对量化噪声有高通作用。因此,模拟滤波器在 Σ-Δ 调制器模型中执行噪声整形功能。

|

||||

```

|

||||

|

||||

|

||||

|

||||

```

|

||||

多级噪声整形 (MASH)

|

||||

```

|

||||

|

||||

|

||||

|

||||

|

||||

|

||||

### 研究方案

|

||||

|

||||

1. 研究目标

|

||||

|

||||

比较现有不同校准算法性能及功耗,针对adc片上校准系统做面积和功耗优化

|

||||

比较现有不同校准算法性能及功耗,针对adc片上校准系统做校准精度、面积、功耗优化

|

||||

|

||||

2. 研究内容

|

||||

|

||||

@ -243,6 +278,8 @@

|

||||

|

||||

[1] Shu Y S . Background digital calibration techniques for high-speed, high resolution analog-to-digital data converters[J]. Dissertations & Theses, 2008. [>>>](https://public.veypi.com/research/digitalcalibration/citations/Background%20digital%20calibration%20techniques%20for%20high-speed%2C%20high%20resolution%20analog-to-digital%20data%20converters.pdf)

|

||||

|

||||

[1] B lecker, E. B , Mcdonald T M , Erdogan O E , et al. Digital Background Calibration of an Algorithmic Analog-to-Digital Converter Using a Simplified Queue[J]. IEEE Journal of Solid-State Circuits, 2003, 38(6):p.1059-1062.

|

||||

|

||||

[1] [数据转换器学习与设计](https://www.zhihu.com/column/c_1308071540374753280)

|

||||

|

||||

[1] [Time-Interleaved Analog-to-Digital Converters](Time-Interleaved Analog-to-Digital Converters)

|

||||

@ -251,7 +288,6 @@

|

||||

- [adc category](https://blog.csdn.net/ZQ07506149/article/details/82557492)

|

||||

- [adc error](https://www.21ic.com/article/849518.html)

|

||||

- [∑–△](https://www.cnblogs.com/nevel/p/6152340.html)

|

||||

|

||||

- [Taking the Mystery out of the Infamous Formula, "SNR = 6.02N + 1.76dB," and Why You Should Care](https://www.analog.com/media/en/training-seminars/tutorials/MT-001.pdf)

|

||||

- [What the Nyquist Criterion Means to Your Sampled Data System Design ](https://www.analog.com/media/en/training-seminars/tutorials/MT-002.pdf)

|

||||

- [Understand SINAD, ENOB, SNR, THD, THD + N, and SFDR so You Don't Get Lost in the Noise Floor ](https://www.analog.com/media/en/training-seminars/tutorials/MT-003.pdf)

|

||||

@ -263,3 +299,8 @@

|

||||

- [Data Converter Codes—Can You Decode Them?](https://www.analog.com/media/en/training-seminars/tutorials/MT-009.pdf)

|

||||

- [The Importance of Data Converter Static Specifications— Don't Lose Sight of the Basics!](https://www.analog.com/media/en/training-seminars/tutorials/MT-010.pdf)

|

||||

- [Find Those Elusive ADC Sparkle Codes and Metastable States ](https://www.analog.com/media/en/training-seminars/tutorials/MT-011.pdf)

|

||||

- [隔离](https://www.analog.com/en/analog-dialogue/raqs/raq-issue-189.html)

|

||||

|

||||

- [行业分析](https://finance.sina.com.cn/stock/stockzmt/2021-08-07/doc-ikqciyzm0070703.shtml)

|

||||

- [An Inside Look at High-Speed ADC Accuracy](https://www.electronicdesign.com/technologies/adc/article/21800833/an-inside-look-at-highspeed-adc-accuracy)

|

||||

|

||||

|

||||

@ -32,4 +32,9 @@

|

||||

- [Voltage-to-Frequency Converters](https://www.analog.com/media/en/training-seminars/tutorials/MT-028.pdf)

|

||||

- [Optical Encoders ](https://www.analog.com/media/en/training-seminars/tutorials/MT-029.pdf)

|

||||

- [Resolver-to-Digital Converters](https://www.analog.com/media/en/training-seminars/tutorials/MT-030.pdf)

|

||||

- [Grounding Data Converters and Solving the Mystery of "AGND" and "DGND" ](https://www.analog.com/media/en/training-seminars/tutorials/MT-031.pdf)

|

||||

- [Grounding Data Converters and Solving the Mystery of "AGND" and "DGND" ](https://www.analog.com/media/en/training-seminars/tutorials/MT-031.pdf)

|

||||

|

||||

[sigma delta ADC原理分析](https://blog.csdn.net/qq_39815222/article/details/103248394)

|

||||

|

||||

[sigma delta 理解程序](https://www.analog.com/en/design-center/interactive-design-tools/sigma-delta-adc-tutorial.html)

|

||||

|

||||

|

||||

95

src/divider/intDivider.v

Normal file

95

src/divider/intDivider.v

Normal file

@ -0,0 +1,95 @@

|

||||

module div_fsm

|

||||

#(

|

||||

parameter DATAWIDTH=8

|

||||

)

|

||||

(

|

||||

input clk ,

|

||||

input rstn ,

|

||||

input en ,

|

||||

output wire ready ,

|

||||

input [DATAWIDTH-1:0] dividend ,

|

||||

input [DATAWIDTH-1:0] divisor ,

|

||||

output wire [DATAWIDTH-1:0] quotient ,

|

||||

output wire [DATAWIDTH-1:0] remainder,

|

||||

output wire vld_out

|

||||

);

|

||||

|

||||

reg [DATAWIDTH*2-1:0] dividend_e ;

|

||||

reg [DATAWIDTH*2-1:0] divisor_e ;

|

||||

reg [DATAWIDTH-1:0] quotient_e ;

|

||||

reg [DATAWIDTH-1:0] remainder_e;

|

||||

|

||||

|

||||

reg [1:0] current_state,next_state;

|

||||

|

||||

reg [DATAWIDTH-1:0] count;

|

||||

|

||||

parameter IDLE =2'b00 ,

|

||||

SUB =2'b01 ,

|

||||

SHIFT=2'b10 ,

|

||||

DONE =2'b11 ;

|

||||

|

||||

|

||||

|

||||

always@(posedge clk or negedge rstn)

|

||||

if(!rstn) current_state <= IDLE;

|

||||

else current_state <= next_state;

|

||||

|

||||

always @(*) begin

|

||||

next_state <= 2'bx;

|

||||

case(current_state)

|

||||

IDLE: if(en) next_state <= SUB;

|

||||

else next_state <= IDLE;

|

||||

SUB: next_state <= SHIFT;

|

||||

SHIFT:if(count<DATAWIDTH) next_state <= SUB;

|

||||

else next_state <= DONE;

|

||||

DONE: next_state <= IDLE;

|

||||

endcase

|

||||

end

|

||||

|

||||

|

||||

always@(posedge clk or negedge rstn) begin

|

||||

if(!rstn)begin

|

||||

dividend_e <= 0;

|

||||

divisor_e <= 0;

|

||||

quotient_e <= 0;

|

||||

remainder_e <= 0;

|

||||

count <= 0;

|

||||

end

|

||||

else begin

|

||||

case(current_state)

|

||||

IDLE:begin

|

||||

dividend_e <= {{DATAWIDTH{1'b0}},dividend};

|

||||

divisor_e <= {divisor,{DATAWIDTH{1'b0}}};

|

||||

end

|

||||

SUB:begin

|

||||

if(dividend_e>=divisor_e)begin

|

||||

quotient_e <= {quotient_e[DATAWIDTH-2:0],1'b1};

|

||||

dividend_e <= dividend_e-divisor_e;

|

||||

end

|

||||

else begin

|

||||

quotient_e <= {quotient_e[DATAWIDTH-2:0],1'b0};

|

||||

dividend_e <= dividend_e;

|

||||

end

|

||||

end

|

||||

SHIFT:begin

|

||||

if(count<DATAWIDTH)begin

|

||||

dividend_e <= dividend_e<<1;

|

||||

count <= count+1;

|

||||

end

|

||||

else begin

|

||||

remainder_e <= dividend_e[DATAWIDTH*2-1:DATAWIDTH];

|

||||

end

|

||||

end

|

||||

DONE:begin

|

||||

count <= 0;

|

||||

end

|

||||

endcase

|

||||

end

|

||||

end

|

||||

|

||||

assign quotient = quotient_e;

|

||||

assign remainder = remainder_e;

|

||||

assign ready=(current_state==IDLE)? 1'b1:1'b0;

|

||||

assign vld_out=(current_state==DONE)? 1'b1:1'b0;

|

||||

endmodule

|

||||

355

src/divider/test.vvp

Executable file

355

src/divider/test.vvp

Executable file

@ -0,0 +1,355 @@

|

||||

#! /usr/local/Cellar/icarus-verilog/11.0/bin/vvp

|

||||

:ivl_version "11.0 (stable)";

|

||||

:ivl_delay_selection "TYPICAL";

|

||||

:vpi_time_precision - 12;

|

||||

:vpi_module "/usr/local/Cellar/icarus-verilog/11.0/lib/ivl/system.vpi";

|

||||

:vpi_module "/usr/local/Cellar/icarus-verilog/11.0/lib/ivl/vhdl_sys.vpi";

|

||||

:vpi_module "/usr/local/Cellar/icarus-verilog/11.0/lib/ivl/vhdl_textio.vpi";

|

||||

:vpi_module "/usr/local/Cellar/icarus-verilog/11.0/lib/ivl/v2005_math.vpi";

|

||||

:vpi_module "/usr/local/Cellar/icarus-verilog/11.0/lib/ivl/va_math.vpi";

|

||||

S_0x7f8221f04500 .scope module, "div_int_tb" "div_int_tb" 2 4;

|

||||

.timescale -9 -12;

|

||||

P_0x600000c48240 .param/l "DATAWIDTH" 0 2 6, +C4<00000000000000000000000000010000>;

|

||||

v0x600002b4cd80_0 .var "clk", 0 0;

|

||||

v0x600002b4ce10_0 .var "dividend", 15 0;

|

||||

v0x600002b4cea0_0 .var "divisor", 15 0;

|

||||

v0x600002b4cf30_0 .var "en", 0 0;

|

||||

v0x600002b4cfc0_0 .var/i "i", 31 0;

|

||||

v0x600002b4d050_0 .net "quotient", 15 0, L_0x600003248230; 1 drivers

|

||||

v0x600002b4d0e0_0 .net "quotient_ref", 15 0, L_0x6000028480a0; 1 drivers

|

||||

v0x600002b4d170_0 .net "ready", 0 0, L_0x600002848280; 1 drivers

|

||||

v0x600002b4d200_0 .net "remainder", 15 0, L_0x6000032482a0; 1 drivers

|

||||

v0x600002b4d290_0 .net "remainder_ref", 15 0, L_0x600002848140; 1 drivers

|

||||

v0x600002b4d320_0 .var "rstn", 0 0;

|

||||

v0x600002b4d3b0_0 .net "vld_out", 0 0, L_0x6000028483c0; 1 drivers

|

||||

E_0x6000017482a0 .event edge, v0x600002b4ccf0_0;

|

||||

E_0x6000017482d0 .event edge, v0x600002b4cab0_0;

|

||||

E_0x600001748300 .event posedge, v0x600002b4c480_0;

|

||||

L_0x6000028480a0 .arith/div 16, v0x600002b4ce10_0, v0x600002b4cea0_0;

|

||||

L_0x600002848140 .arith/mod 16, v0x600002b4ce10_0, v0x600002b4cea0_0;

|

||||

S_0x7f8221f04670 .scope module, "U_DIV_FSM_0" "div_fsm" 2 53, 3 1 0, S_0x7f8221f04500;

|

||||

.timescale -9 -12;

|

||||

.port_info 0 /INPUT 1 "clk";

|

||||

.port_info 1 /INPUT 1 "rstn";

|

||||

.port_info 2 /INPUT 1 "en";

|

||||

.port_info 3 /OUTPUT 1 "ready";

|

||||

.port_info 4 /INPUT 16 "dividend";

|

||||

.port_info 5 /INPUT 16 "divisor";

|

||||

.port_info 6 /OUTPUT 16 "quotient";

|

||||

.port_info 7 /OUTPUT 16 "remainder";

|

||||

.port_info 8 /OUTPUT 1 "vld_out";

|

||||

P_0x7f8221f047e0 .param/l "DATAWIDTH" 0 3 3, +C4<00000000000000000000000000010000>;

|

||||

P_0x7f8221f04820 .param/l "DONE" 0 3 30, C4<11>;

|

||||

P_0x7f8221f04860 .param/l "IDLE" 0 3 27, C4<00>;

|

||||

P_0x7f8221f048a0 .param/l "SHIFT" 0 3 29, C4<10>;

|

||||

P_0x7f8221f048e0 .param/l "SUB" 0 3 28, C4<01>;

|

||||

L_0x600003248230 .functor BUFZ 16, v0x600002b4ca20_0, C4<0000000000000000>, C4<0000000000000000>, C4<0000000000000000>;

|

||||

L_0x6000032482a0 .functor BUFZ 16, v0x600002b4cbd0_0, C4<0000000000000000>, C4<0000000000000000>, C4<0000000000000000>;

|

||||

L_0x7f8228050098 .functor BUFT 1, C4<0>, C4<0>, C4<0>, C4<0>;

|

||||

v0x600002b4c000_0 .net/2u *"_ivl_10", 0 0, L_0x7f8228050098; 1 drivers

|

||||

L_0x7f82280500e0 .functor BUFT 1, C4<11>, C4<0>, C4<0>, C4<0>;

|

||||

v0x600002b4c090_0 .net/2u *"_ivl_14", 1 0, L_0x7f82280500e0; 1 drivers

|

||||

v0x600002b4c120_0 .net *"_ivl_16", 0 0, L_0x600002848320; 1 drivers

|

||||

L_0x7f8228050128 .functor BUFT 1, C4<1>, C4<0>, C4<0>, C4<0>;

|

||||

v0x600002b4c1b0_0 .net/2u *"_ivl_18", 0 0, L_0x7f8228050128; 1 drivers

|

||||

L_0x7f8228050170 .functor BUFT 1, C4<0>, C4<0>, C4<0>, C4<0>;

|

||||

v0x600002b4c240_0 .net/2u *"_ivl_20", 0 0, L_0x7f8228050170; 1 drivers

|

||||

L_0x7f8228050008 .functor BUFT 1, C4<00>, C4<0>, C4<0>, C4<0>;

|

||||

v0x600002b4c2d0_0 .net/2u *"_ivl_4", 1 0, L_0x7f8228050008; 1 drivers

|

||||

v0x600002b4c360_0 .net *"_ivl_6", 0 0, L_0x6000028481e0; 1 drivers

|

||||

L_0x7f8228050050 .functor BUFT 1, C4<1>, C4<0>, C4<0>, C4<0>;

|

||||

v0x600002b4c3f0_0 .net/2u *"_ivl_8", 0 0, L_0x7f8228050050; 1 drivers

|

||||

v0x600002b4c480_0 .net "clk", 0 0, v0x600002b4cd80_0; 1 drivers

|

||||

v0x600002b4c510_0 .var "count", 15 0;

|

||||

v0x600002b4c5a0_0 .var "current_state", 1 0;

|

||||

v0x600002b4c630_0 .net "dividend", 15 0, v0x600002b4ce10_0; 1 drivers

|

||||

v0x600002b4c6c0_0 .var "dividend_e", 31 0;

|

||||

v0x600002b4c750_0 .net "divisor", 15 0, v0x600002b4cea0_0; 1 drivers

|

||||

v0x600002b4c7e0_0 .var "divisor_e", 31 0;

|

||||

v0x600002b4c870_0 .net "en", 0 0, v0x600002b4cf30_0; 1 drivers

|

||||

v0x600002b4c900_0 .var "next_state", 1 0;

|

||||

v0x600002b4c990_0 .net "quotient", 15 0, L_0x600003248230; alias, 1 drivers

|

||||

v0x600002b4ca20_0 .var "quotient_e", 15 0;

|

||||

v0x600002b4cab0_0 .net "ready", 0 0, L_0x600002848280; alias, 1 drivers

|

||||

v0x600002b4cb40_0 .net "remainder", 15 0, L_0x6000032482a0; alias, 1 drivers

|

||||

v0x600002b4cbd0_0 .var "remainder_e", 15 0;

|

||||

v0x600002b4cc60_0 .net "rstn", 0 0, v0x600002b4d320_0; 1 drivers

|

||||

v0x600002b4ccf0_0 .net "vld_out", 0 0, L_0x6000028483c0; alias, 1 drivers

|

||||

E_0x600001748330/0 .event negedge, v0x600002b4cc60_0;

|

||||

E_0x600001748330/1 .event posedge, v0x600002b4c480_0;

|

||||

E_0x600001748330 .event/or E_0x600001748330/0, E_0x600001748330/1;

|

||||

E_0x600001748360 .event edge, v0x600002b4c5a0_0, v0x600002b4c870_0, v0x600002b4c510_0;

|

||||

L_0x6000028481e0 .cmp/eq 2, v0x600002b4c5a0_0, L_0x7f8228050008;

|

||||

L_0x600002848280 .functor MUXZ 1, L_0x7f8228050098, L_0x7f8228050050, L_0x6000028481e0, C4<>;

|

||||

L_0x600002848320 .cmp/eq 2, v0x600002b4c5a0_0, L_0x7f82280500e0;

|

||||

L_0x6000028483c0 .functor MUXZ 1, L_0x7f8228050170, L_0x7f8228050128, L_0x600002848320, C4<>;

|

||||

.scope S_0x7f8221f04670;

|

||||

T_0 ;

|

||||

%wait E_0x600001748330;

|

||||

%load/vec4 v0x600002b4cc60_0;

|

||||

%nor/r;

|

||||

%flag_set/vec4 8;

|

||||

%jmp/0xz T_0.0, 8;

|

||||

%pushi/vec4 0, 0, 2;

|

||||

%assign/vec4 v0x600002b4c5a0_0, 0;

|

||||

%jmp T_0.1;

|

||||

T_0.0 ;

|

||||

%load/vec4 v0x600002b4c900_0;

|

||||

%assign/vec4 v0x600002b4c5a0_0, 0;

|

||||

T_0.1 ;

|

||||

%jmp T_0;

|

||||

.thread T_0;

|

||||

.scope S_0x7f8221f04670;

|

||||

T_1 ;

|

||||

%wait E_0x600001748360;

|

||||

%pushi/vec4 3, 3, 2;

|

||||

%assign/vec4 v0x600002b4c900_0, 0;

|

||||

%load/vec4 v0x600002b4c5a0_0;

|

||||

%dup/vec4;

|

||||

%pushi/vec4 0, 0, 2;

|

||||

%cmp/u;

|

||||

%jmp/1 T_1.0, 6;

|

||||

%dup/vec4;

|

||||

%pushi/vec4 1, 0, 2;

|

||||

%cmp/u;

|

||||

%jmp/1 T_1.1, 6;

|

||||

%dup/vec4;

|

||||

%pushi/vec4 2, 0, 2;

|

||||

%cmp/u;

|

||||

%jmp/1 T_1.2, 6;

|

||||

%dup/vec4;

|

||||

%pushi/vec4 3, 0, 2;

|

||||

%cmp/u;

|

||||

%jmp/1 T_1.3, 6;

|

||||

%jmp T_1.4;

|

||||

T_1.0 ;

|

||||

%load/vec4 v0x600002b4c870_0;

|

||||

%flag_set/vec4 8;

|

||||

%jmp/0xz T_1.5, 8;

|

||||

%pushi/vec4 1, 0, 2;

|

||||

%assign/vec4 v0x600002b4c900_0, 0;

|

||||

%jmp T_1.6;

|

||||

T_1.5 ;

|

||||

%pushi/vec4 0, 0, 2;

|

||||

%assign/vec4 v0x600002b4c900_0, 0;

|

||||

T_1.6 ;

|

||||

%jmp T_1.4;

|

||||

T_1.1 ;

|

||||

%pushi/vec4 2, 0, 2;

|

||||

%assign/vec4 v0x600002b4c900_0, 0;

|

||||

%jmp T_1.4;

|

||||

T_1.2 ;

|

||||

%load/vec4 v0x600002b4c510_0;

|

||||

%pad/u 32;

|

||||

%cmpi/u 16, 0, 32;

|

||||

%jmp/0xz T_1.7, 5;

|

||||

%pushi/vec4 1, 0, 2;

|

||||

%assign/vec4 v0x600002b4c900_0, 0;

|

||||

%jmp T_1.8;

|

||||

T_1.7 ;

|

||||

%pushi/vec4 3, 0, 2;

|

||||

%assign/vec4 v0x600002b4c900_0, 0;

|

||||

T_1.8 ;

|

||||

%jmp T_1.4;

|

||||

T_1.3 ;

|

||||

%pushi/vec4 0, 0, 2;

|

||||

%assign/vec4 v0x600002b4c900_0, 0;

|

||||

%jmp T_1.4;

|

||||

T_1.4 ;

|

||||

%pop/vec4 1;

|

||||

%jmp T_1;

|

||||

.thread T_1, $push;

|

||||

.scope S_0x7f8221f04670;

|

||||

T_2 ;

|

||||

%wait E_0x600001748330;

|

||||

%load/vec4 v0x600002b4cc60_0;

|

||||

%nor/r;

|

||||

%flag_set/vec4 8;

|

||||

%jmp/0xz T_2.0, 8;

|

||||

%pushi/vec4 0, 0, 32;

|

||||

%assign/vec4 v0x600002b4c6c0_0, 0;

|

||||

%pushi/vec4 0, 0, 32;

|

||||

%assign/vec4 v0x600002b4c7e0_0, 0;

|

||||

%pushi/vec4 0, 0, 16;

|

||||

%assign/vec4 v0x600002b4ca20_0, 0;

|

||||

%pushi/vec4 0, 0, 16;

|

||||

%assign/vec4 v0x600002b4cbd0_0, 0;

|

||||

%pushi/vec4 0, 0, 16;

|

||||

%assign/vec4 v0x600002b4c510_0, 0;

|

||||

%jmp T_2.1;

|

||||

T_2.0 ;

|

||||

%load/vec4 v0x600002b4c5a0_0;

|

||||

%dup/vec4;

|

||||

%pushi/vec4 0, 0, 2;

|

||||

%cmp/u;

|

||||

%jmp/1 T_2.2, 6;

|

||||

%dup/vec4;

|

||||

%pushi/vec4 1, 0, 2;

|

||||

%cmp/u;

|

||||

%jmp/1 T_2.3, 6;

|

||||

%dup/vec4;

|

||||

%pushi/vec4 2, 0, 2;

|

||||

%cmp/u;

|

||||

%jmp/1 T_2.4, 6;

|

||||

%dup/vec4;

|

||||

%pushi/vec4 3, 0, 2;

|

||||

%cmp/u;

|

||||

%jmp/1 T_2.5, 6;

|

||||

%jmp T_2.6;

|

||||

T_2.2 ;

|

||||

%pushi/vec4 0, 0, 16;

|

||||

%load/vec4 v0x600002b4c630_0;

|

||||

%concat/vec4; draw_concat_vec4

|

||||

%assign/vec4 v0x600002b4c6c0_0, 0;

|

||||

%load/vec4 v0x600002b4c750_0;

|

||||

%concati/vec4 0, 0, 16;

|

||||

%assign/vec4 v0x600002b4c7e0_0, 0;

|

||||

%jmp T_2.6;

|

||||

T_2.3 ;

|

||||

%load/vec4 v0x600002b4c7e0_0;

|

||||

%load/vec4 v0x600002b4c6c0_0;

|

||||

%cmp/u;

|

||||

%flag_or 5, 4;

|

||||

%jmp/0xz T_2.7, 5;

|

||||

%load/vec4 v0x600002b4ca20_0;

|

||||

%parti/s 15, 0, 2;

|

||||

%concati/vec4 1, 0, 1;

|

||||

%assign/vec4 v0x600002b4ca20_0, 0;

|

||||

%load/vec4 v0x600002b4c6c0_0;

|

||||

%load/vec4 v0x600002b4c7e0_0;

|

||||

%sub;

|

||||

%assign/vec4 v0x600002b4c6c0_0, 0;

|

||||

%jmp T_2.8;

|

||||

T_2.7 ;

|

||||

%load/vec4 v0x600002b4ca20_0;

|

||||

%parti/s 15, 0, 2;

|

||||

%concati/vec4 0, 0, 1;

|

||||

%assign/vec4 v0x600002b4ca20_0, 0;

|

||||

%load/vec4 v0x600002b4c6c0_0;

|

||||

%assign/vec4 v0x600002b4c6c0_0, 0;

|

||||

T_2.8 ;

|

||||

%jmp T_2.6;

|

||||

T_2.4 ;

|

||||

%load/vec4 v0x600002b4c510_0;

|

||||

%pad/u 32;

|

||||

%cmpi/u 16, 0, 32;

|

||||

%jmp/0xz T_2.9, 5;

|

||||

%load/vec4 v0x600002b4c6c0_0;

|

||||

%ix/load 4, 1, 0;

|

||||

%flag_set/imm 4, 0;

|

||||

%shiftl 4;

|

||||

%assign/vec4 v0x600002b4c6c0_0, 0;

|

||||

%load/vec4 v0x600002b4c510_0;

|

||||

%addi 1, 0, 16;

|

||||

%assign/vec4 v0x600002b4c510_0, 0;

|

||||

%jmp T_2.10;

|

||||

T_2.9 ;

|

||||

%load/vec4 v0x600002b4c6c0_0;

|

||||

%parti/s 16, 16, 6;

|

||||

%assign/vec4 v0x600002b4cbd0_0, 0;

|

||||

T_2.10 ;

|

||||

%jmp T_2.6;

|

||||

T_2.5 ;

|

||||

%pushi/vec4 0, 0, 16;

|

||||

%assign/vec4 v0x600002b4c510_0, 0;

|

||||

%jmp T_2.6;

|

||||

T_2.6 ;

|

||||

%pop/vec4 1;

|

||||

T_2.1 ;

|

||||

%jmp T_2;

|

||||

.thread T_2;

|

||||

.scope S_0x7f8221f04500;

|

||||

T_3 ;

|

||||

%delay 1000, 0;

|

||||

%load/vec4 v0x600002b4cd80_0;

|

||||

%inv;

|

||||

%store/vec4 v0x600002b4cd80_0, 0, 1;

|

||||

%jmp T_3;

|

||||

.thread T_3;

|

||||

.scope S_0x7f8221f04500;

|

||||

T_4 ;

|

||||

%pushi/vec4 1, 0, 1;

|

||||

%store/vec4 v0x600002b4cd80_0, 0, 1;

|

||||

%pushi/vec4 1, 0, 1;

|

||||

%store/vec4 v0x600002b4d320_0, 0, 1;

|

||||

%pushi/vec4 0, 0, 1;

|

||||

%store/vec4 v0x600002b4cf30_0, 0, 1;

|

||||

%delay 2000, 0;

|

||||

%pushi/vec4 0, 0, 1;

|

||||

%store/vec4 v0x600002b4d320_0, 0, 1;

|

||||

%delay 2000, 0;

|

||||

%pushi/vec4 1, 0, 1;

|

||||

%store/vec4 v0x600002b4d320_0, 0, 1;

|

||||

%pushi/vec4 2, 0, 32;

|

||||

T_4.0 %dup/vec4;

|

||||

%pushi/vec4 0, 0, 32;

|

||||

%cmp/s;

|

||||

%jmp/1xz T_4.1, 5;

|

||||

%jmp/1 T_4.1, 4;

|

||||

%pushi/vec4 1, 0, 32;

|

||||

%sub;

|

||||

%wait E_0x600001748300;

|

||||

%jmp T_4.0;

|

||||

T_4.1 ;

|

||||

%pop/vec4 1;

|

||||

%pushi/vec4 0, 0, 32;

|

||||

%store/vec4 v0x600002b4cfc0_0, 0, 32;

|

||||

T_4.2 ;

|

||||

%load/vec4 v0x600002b4cfc0_0;

|

||||

%cmpi/s 10, 0, 32;

|

||||

%jmp/0xz T_4.3, 5;

|

||||

%pushi/vec4 1, 0, 1;

|

||||

%assign/vec4 v0x600002b4cf30_0, 0;

|

||||

%vpi_func 2 35 "$random" 32 {0 0 0};

|

||||

%pushi/vec4 1000, 0, 32;

|

||||

%mod/s;

|

||||

%pad/s 16;

|

||||

%assign/vec4 v0x600002b4ce10_0, 0;

|

||||

%vpi_func 2 36 "$random" 32 {0 0 0};

|

||||

%pushi/vec4 100, 0, 32;

|

||||

%mod/s;

|

||||

%pad/s 16;

|

||||

%assign/vec4 v0x600002b4cea0_0, 0;

|

||||

T_4.4 ;

|

||||

%load/vec4 v0x600002b4d170_0;

|

||||

%pad/u 32;

|

||||

%pushi/vec4 1, 0, 32;

|

||||

%cmp/e;

|

||||

%flag_get/vec4 4;

|

||||

%cmpi/ne 1, 0, 1;

|

||||

%jmp/0xz T_4.5, 6;

|

||||

%wait E_0x6000017482d0;

|

||||

%jmp T_4.4;

|

||||

T_4.5 ;

|

||||

T_4.6 ;

|

||||

%load/vec4 v0x600002b4d3b0_0;

|

||||

%pad/u 32;

|

||||

%pushi/vec4 1, 0, 32;

|

||||

%cmp/e;

|

||||

%flag_get/vec4 4;

|

||||

%cmpi/ne 1, 0, 1;

|

||||

%jmp/0xz T_4.7, 6;

|

||||

%wait E_0x6000017482a0;

|

||||

%jmp T_4.6;

|

||||

T_4.7 ;

|

||||

%load/vec4 v0x600002b4cfc0_0;

|

||||

%addi 1, 0, 32;

|

||||

%store/vec4 v0x600002b4cfc0_0, 0, 32;

|

||||

%jmp T_4.2;

|

||||

T_4.3 ;

|

||||

%end;

|

||||

.thread T_4;

|

||||

.scope S_0x7f8221f04500;

|

||||

T_5 ;

|

||||

%vpi_call 2 46 "$dumpfile", "test.vcd" {0 0 0};

|

||||

%vpi_call 2 47 "$dumpvars", 32'sb00000000000000000000000000000000, S_0x7f8221f04500 {0 0 0};

|

||||

%delay 1000000, 0;

|

||||

%vpi_call 2 48 "$finish" {0 0 0};

|

||||

%end;

|

||||

.thread T_5;

|

||||

# The file index is used to find the file name in the following table.

|

||||

:file_names 4;

|

||||

"N/A";

|

||||

"<interactive>";

|

||||

"testIntDivider.v";

|

||||

"./intDivider.v";

|

||||

65

src/divider/testIntDivider.v

Normal file

65

src/divider/testIntDivider.v

Normal file

@ -0,0 +1,65 @@

|

||||

`timescale 1ns/1ps

|

||||

`include "intDivider.v"

|

||||

|

||||

module div_int_tb();

|

||||

|

||||

parameter DATAWIDTH = 16;

|

||||

|

||||

reg clk;

|

||||

reg rstn;

|

||||

reg en;

|

||||

wire ready;

|

||||

reg [DATAWIDTH-1:0] dividend;

|

||||

reg [DATAWIDTH-1:0] divisor;

|

||||

wire [DATAWIDTH-1:0] quotient;

|

||||

wire [DATAWIDTH-1:0] remainder;

|

||||

wire vld_out;

|

||||

|

||||

wire [DATAWIDTH-1:0] quotient_ref; // true result

|

||||

wire [DATAWIDTH-1:0] remainder_ref;

|

||||

assign quotient_ref = dividend/divisor;

|

||||

assign remainder_ref = dividend%divisor;

|

||||

|

||||

always #1 clk = ~clk;

|

||||

|

||||

integer i;

|

||||

initial begin

|

||||

clk = 1;

|

||||

rstn = 1;

|

||||

en = 0;

|

||||

#2 rstn = 0; #2 rstn = 1;

|

||||

repeat(2) @(posedge clk);

|

||||

|

||||

for(i=0;i<10;i=i+1) begin

|

||||

en <= 1;

|

||||

dividend <= $random%1000;

|

||||

divisor <= $random%100;

|

||||

wait (ready == 1);

|

||||

wait (vld_out == 1);

|

||||

end

|

||||

|

||||

|

||||

end

|

||||

|

||||

|

||||

initial begin

|

||||

$dumpfile("test.vcd");

|

||||

$dumpvars(0, div_int_tb);

|

||||

#1000 $finish;

|

||||

end

|

||||

|

||||

div_fsm #(

|

||||

.DATAWIDTH ( DATAWIDTH ))

|

||||

U_DIV_FSM_0(

|

||||

.clk ( clk ),

|

||||

.rstn ( rstn ),

|

||||

.en ( en ),

|

||||

.ready ( ready ),

|

||||

.dividend ( dividend ),

|

||||

.divisor ( divisor ),

|

||||

.quotient ( quotient ),

|

||||

.remainder ( remainder ),

|

||||

.vld_out ( vld_out )

|

||||

);

|

||||

|

||||

endmodule

|

||||

Loading…

x

Reference in New Issue

Block a user