针对adc的片上数字校准系统研究

研究意义

模数转换器是各种数字系统中不可缺少的组成部分,其性能的优劣直接关系整体系统的性能和功能发挥,随着处理器和信号处理技术的不断发展,对adc的性能要求也越来越高,高速高精度已成为信号处理领域必要要求。但是,随着流水线ADC的精度提高的12bit以上时,工艺的偏差导致的电容失配、运放的非理想性等误差使得ADC的精度收到了限制,通过传统模拟电路的设计方法已无法设计出符合要求的高精高速ADC。为实现ADC的高精度,采用数字校准的方法对采集的数据进行误差校准,由于其鲁棒性、灵活性且不打断AD转换,可以有效补偿工艺偏差带来的系统误差,提高流水线ADC的性能。

研究现状分析

ADC 分类

-

并行ADC

并行结构的数据转换器的基本思想是:同时比较待转换的信号电平与所有级别的量化电平之间的关系,在模拟信号和数字信号之间相互转换。并行结构所对应的A/D和D/A转换器件分别为Flash-ADC和串状DAC。

Flash-ADC内含一列并联比较器,一列由电阻分压器产生的电平作为相应的比较器的基准电压。被转换的模拟电压信号同时加到全部比较器上,各比较器的输出经编码后作为ADC的输出,如图2.12所示。

一个分辨率为N(bit)的Flash-ADC含有2N个精密电阻,2N−1个高速比较器;分辨率每增加1bit,需要增加2N个精密电阻和2N个高速比较器,这会大大增加集成的复杂度和器件功耗。因此一般Flash-ADC的分辨率无法达到很高。

串状DAC是实现Flash-ADC的逆操作,因使用电阻串来构造参考电压而得名,在有的书中也被称为开尔文分配器。串状DAC依靠待转换数据来控制一组开关,以产生合适的电流通过精密电阻,从而产生合适的模拟信号电压。

并行结构只需要一级模拟电路,因此具有设计简单,转换时间短,速度快的优点,在所有可能的结构中提供最快的数据转换。在分辨率要求较低的情况下,Flash-ADC和串状DAC两种结构都容易采用超大规模集成电路(VLSI)进行设计。然而,由于比较器(或开关)和精密电阻的数量随着转换器的分辨率呈指数增长,Flash-ADC和串状DAC的芯片面积和功耗也随之呈指数增长。

-

流水线型ADC

在采样率于5msps到10msps之间的应用中,流水线ADC体系结构占主导地位。尽管在20世纪80年代和90年代初,全并行体系结构主导了8 bit video IC ADC市场,但流水线体系结构在现代应用中已基本上取代了闪存ADC。有少量采样率大于1GHz的高功率砷化镓(GaAs)闪存转换器,但分辨率限于6或8位。然而,flash转换器仍然是高分辨率流水线ADC的一个流行构件。

流水线ADC的应用包括视频、图像处理、通信等方面。该体系结构适用于各种成本相对较低的IC工艺,如CMOS和BiCMOS。目前的技术在采样率大于100msps时能达到12到16位的分辨率。

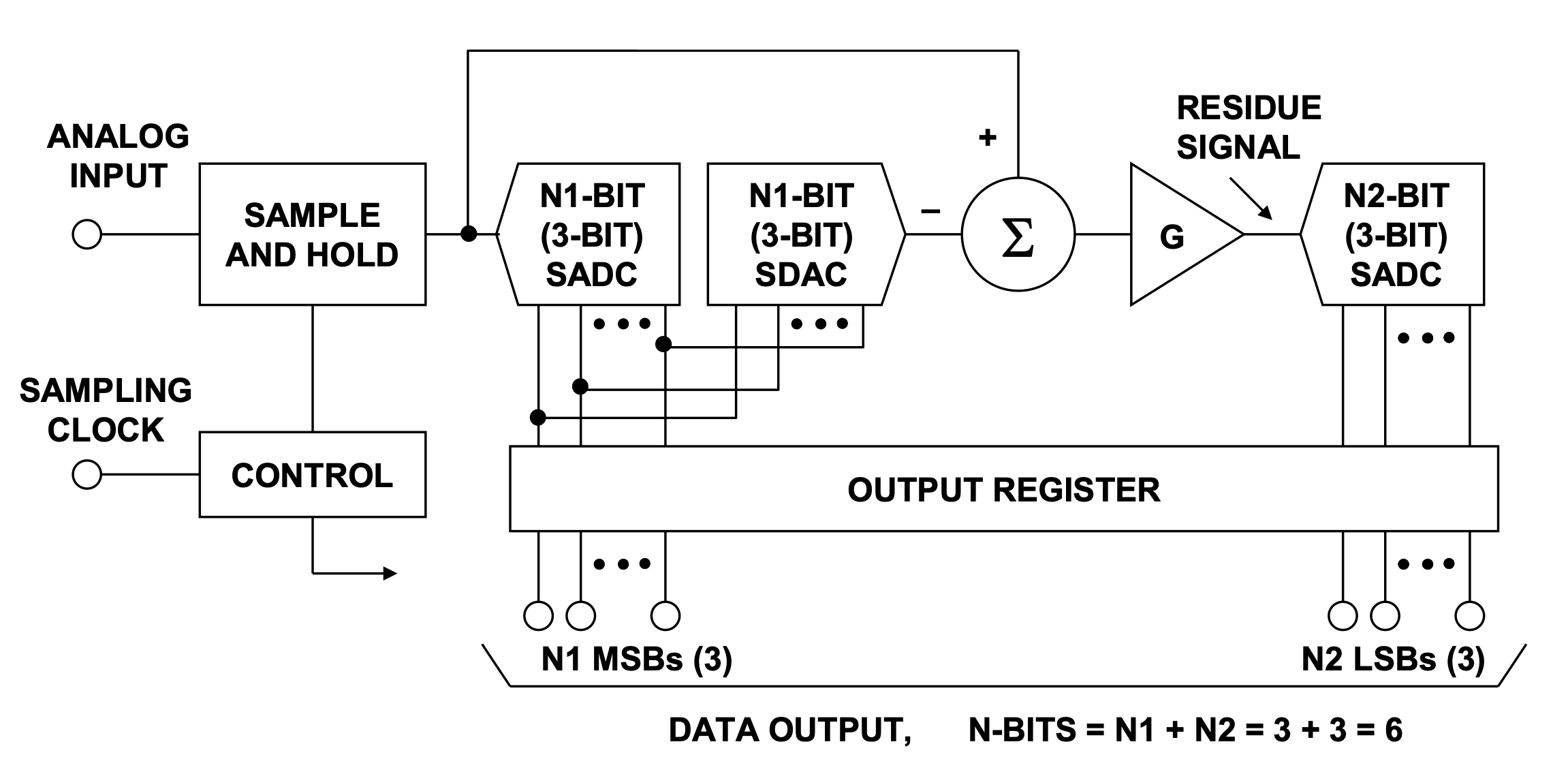

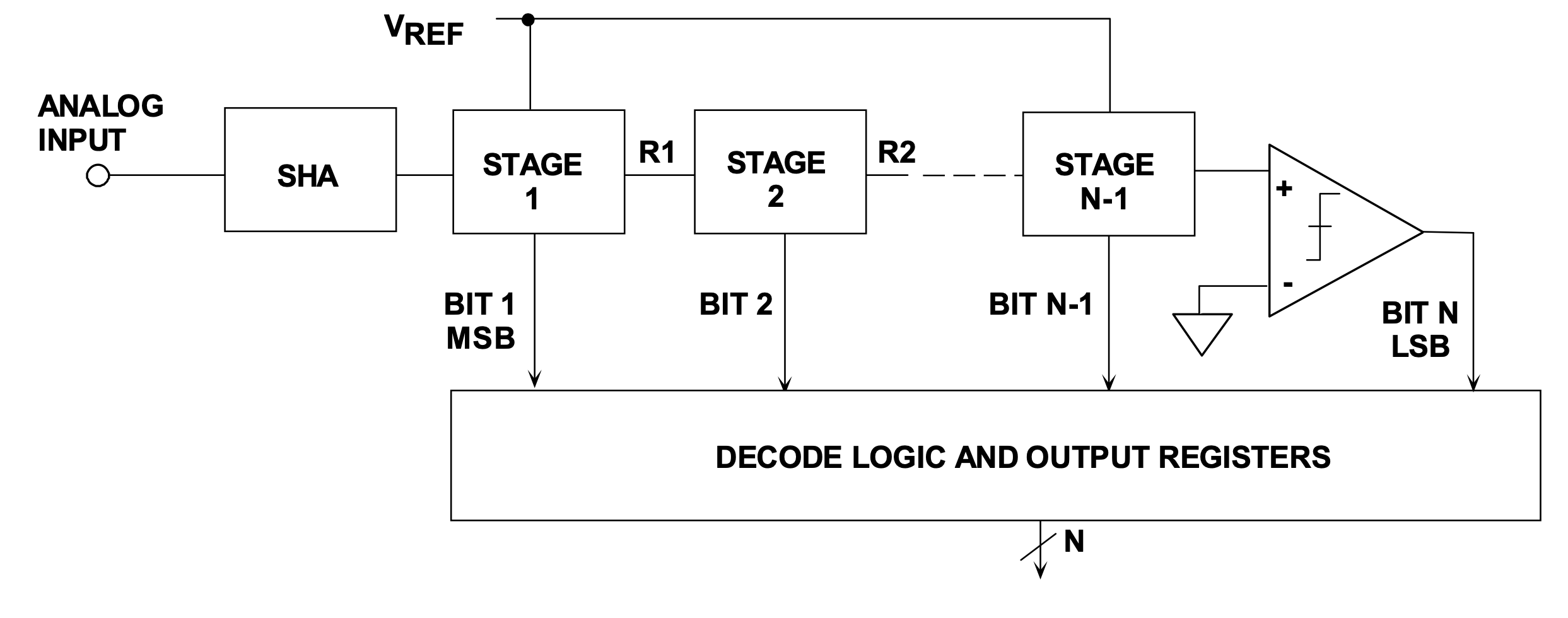

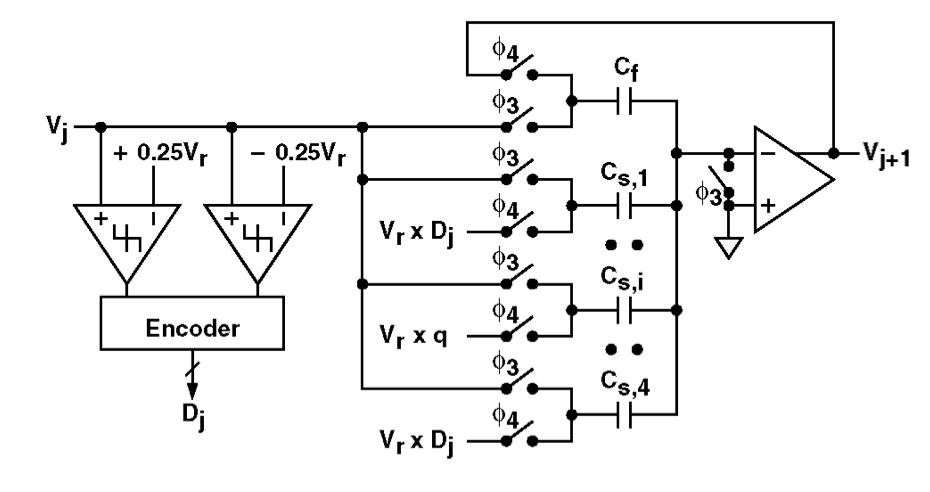

流水线 ADC 通常由 N 个位数相同或不相同的 低分辨率子级组成 ,除最后一级外 ,每个子级都包括 子 ADC 、子 DAC 、减法电路和余量放大器 ,其中子 DAC 、减法电路和余量放大器组合在一起称为 MDAC .

-

逐次逼近型ADC(SAR)

多年来,SAR ADC一直是数据采集系统的主流。最近的设计改进将这些ADC的采样频率扩展到兆赫范围,分辨率为18位。模拟设备PulSAR®系列SAR ADC使用内部开关电容技术和自动校准,并在CMOS工艺上以2 MSPS(AD7641)提供18位,无需昂贵的薄膜激光微调。在16位级别,AD7625(6 MSPS)和AD7626(10 MSPS)也代表了突破性的技术。

SAR ADC 分多步执行转换, 转换步骤数等 于ADC转换器中的位数。每个步骤均由ADC时钟驱动。每个ADC时钟从结果到输出产生一 位。ADC的内部设计基于切换电容技术。

以10bit ADC为例

- 采样状态:电容充电至电压VIN。Sa切换至VIN,采样期间Sb开关闭合

- 保持状态:输入断开,电容保持输入电压。Sb开关打开,然后S1-S11切换至接地且Sa切换至VREF。

- 逐次逼近:第一个逼近步骤。S1切换至VREF。VIN与VREF/2比较。如果MSB = 0,则与¼VREF进行比较,S1切换回接地。S2切换至VREF。如果MSB = 1,则与¾VREF进行比较,S1保持接地。S2切换至VREF。重复如上步骤,直到LSB为止。可以简单理解为二分法逐次进行输入电压与参考电压的比较。首次于VREF/2比较,下次比较根据上次比较结果决定,如果MSB=1则与¾VREF比较。如果MSB=0则与¼VREF比较。后面决定与1/8VREF 3/8VREF、 5/8VREF、 7/8VREF之一做比较。循环直到输出LSB为止。

-

∑–△ ADC

sigma-delta ADC是现代声带、音频和高分辨率精密工业测量应用的首选转换器。高度数字化的体系结构非常适合现代fine-line CMOS工艺,因此可以在不显著增加成本的情况下轻松添加数字功能。由于它的广泛使用,了解这种转换器架构背后的基本原理非常重要。

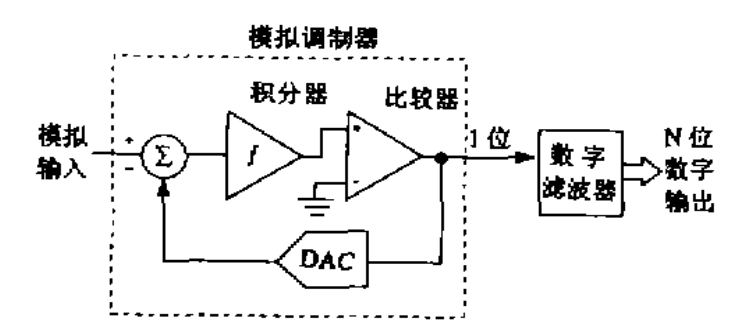

这种ADC又称为过采样转换器,其结构较简单。它由∑–△调制器及连接于其后的数字滤故器构成。调制器的结构近似于双斜率ADC,包括一个积分器和一个比较器,以及含有一个1位DAC的反馈环。这个内置的DAC仅仅是一个开关。它将积分器输入切换到一个正或负的参考电压。∑–△ADC还包括一个时钟单元.为调制器和数字滤波器提供适当的定时。窄带信号送人∑–△ADC后以非常低的分辨率(1位)进行量化,但采样频率却非常高.如2MHz或更高。经过数字滤波处理后 .这种过采样速率被降低到8kHz左右,同时ADC的分辨率(即动态范围 ) 被提高到16位或更高。尽管比流水线ADC慢且输入带宽较窄,∑–△ADC仍具有以下三种优势:

- 低价格、高性能 - 集成化的数字滤波 - 与DSP技术兼容,便于实现系统集成

-

积分型ADC

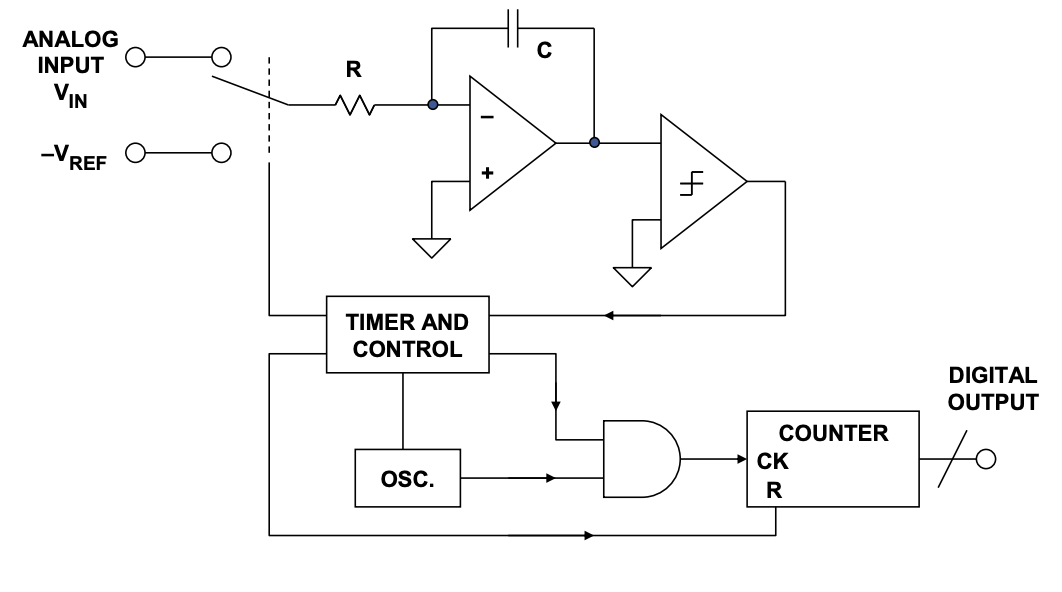

积分型ADC又称双斜率或多斜率数据转换器,是应用最为广泛的转换器类型。经典的双斜率转换器包括两个主要部分:一部分电路采样并量化输入电压.产生一个时域间隔或脉冲序列;再由一个计数器将其转换为数字量输出。双斜率转换器采用一个带有输入切换开头关的模拟积分器,一个比较器和一个计数单元。积分器对输入电压积分固定的时间间隔Tm幢,诙时间间隔通常对应于内部计数单元的最大计数(如图4所示)时间到达后将计数器复位井将积分器输入连接到反极性(负)参考电压。在这个反扳性信号作用下积分器被“反向积分直到括出回到零,井使计数器终止 ,积分器复位。

-

折叠型ADC (Folding ADC)

“折叠”架构使用每比特一级执行A/D转换,总体概念如图1所示。每级一位且无纠错的多级流水线ADC基本上是bit-per-stage转换器。实际上,这种类型的流水线转换器通常使用每级1.5bit的方法来提供错误校正。

ADC性能指标

-

面积

-

功耗

-

动态范围

-

dBFS

-

THD

-

THD/N

-

SNR

-

DAC SETTLING TIME

-

Glitch impulse area

ADC误差分析

要研究ADC数字校准系统,就先要对校准目标有个清晰的认识,明白其误差产生原理,才能针对性去校准误差。 ADC误差主要来源于内部自身转换产生的误差和外部环境造成的误差。

先简单分析下外部环境误差,外部环境并非在生产和研发阶段可以控制的因素,因此也不在片上校准系统校准范围内, 如参考电压噪声、模拟输入信号噪声、ADC动态范围匹配不佳、模拟信号源电阻、注入电流、温度等影响都会对最后转换精度造成影响。

-

量化误差

量化误差是基本误差,用简单3bit ADC来说明。输入电压被数字化,以8个离散电平来划分,分别由代码000b到111b去代表它们,每一代码跨越Vref/8的电压范围。代码大小一般被定义为一个最低有效位(Least Significant Bit,LSB)。若假定Vref=8V时,每个代码之间的电压变换就代表1V。换言之,产生指定代码的实际电压与代表该码的电压两者之间存在误差。一般来说,0.5LSB偏移加入到输入端便导致在理想过渡点上有正负0.5LSB的量化误差。

-

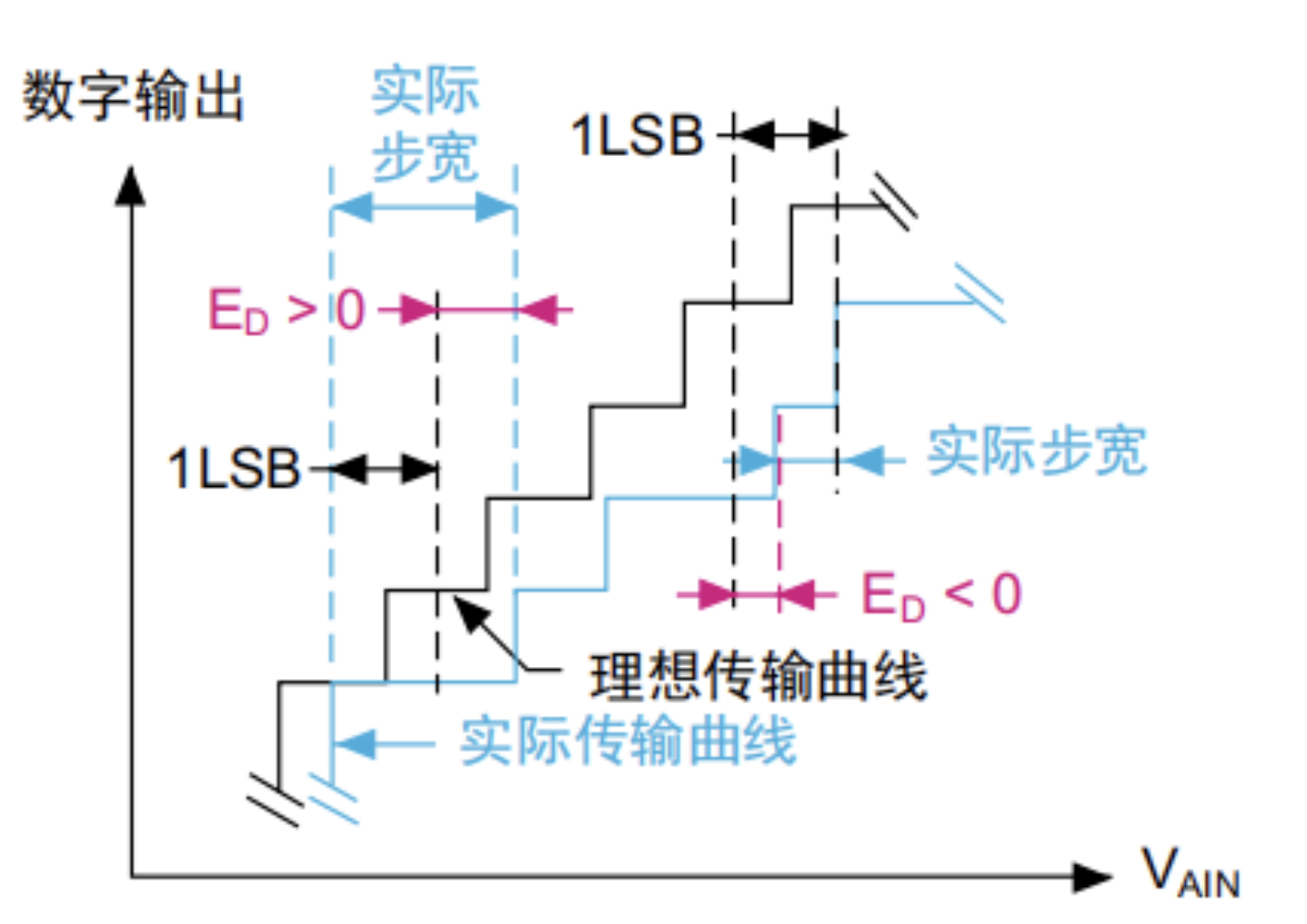

微分非线性误差

微分线性误差(DLE)为实际步进和理想步进之间的最大偏离。这里的“理想情况”不是指理想传输曲线,而是指ADC分辨率。在下图中,用ED表示DLE。

ED = 实际步宽 – 1 LSB

理想情况下,1 LSB的模拟输入电压变化量应导致数字代码变化。如果需要大于1 LSB的模拟输入电压才能导致数字代码变化,将观察到微分线性误差。因此,DLE对应于从一个数字代 码变为下一个数字代码所需的最大额外电压。DLE也称为微分非线性(DLE)误差。

-

积分非线性误差

积分线性误差为任何实际转换和端点相关线间的最大偏离。在下图中,用EL表示ILE。端点相关线可以定义为A/D传输曲线上连接第一次实际转换与最后一次实际转换的线。EL是指与每一次转换的这条线的偏离。因此,端点相关线对应于实际传输曲线并且与理想传输曲线不相关。ILE也称为积分非线性(INL)误差。ILE是整个范围内DLE的积分。

-

增益与偏移误差

偏移误差是第一次实际转换和第一次理想转换之间的偏离。第一次转换发生在数字ADC输出 从0变为1时。理想情况下,当模拟输入介于0.5 LSB和1.5 LSB之间时,数字输出应为1。仍然是理想情况下,第一次转换发生在0.5 LSB处。用EO表示偏移误差。

增益误差是最后一次实际转换和最后一次理想转换之间的偏离。增益误差用EG表示。最后一次实际转换是从0xFFE到0xFFF的转换。理想情况下,当模拟输入等于VREF+ – 0.5 LSB时,应存在从0xFFE到0xFFF的转换。因此对于VREF+= 3.3 V,最后一次理想转换应发生 在3.299597 V处。如果ADC提供VAIN < VREF+ – 0.5 LSB的0xFFF读数,将获得负增益误差。

ADC 校准方案

校准系统分类

-

模拟校准

使用电路补偿器件误差

-

数字校准

-

前台校准

校准时ADC不工作, 结束后切换

-

后台校准

ADC工作同时进行误差校准

-

现有校准方法

-

基于统计的数字校准

-

自适应滤波

-

多项式插值法

-

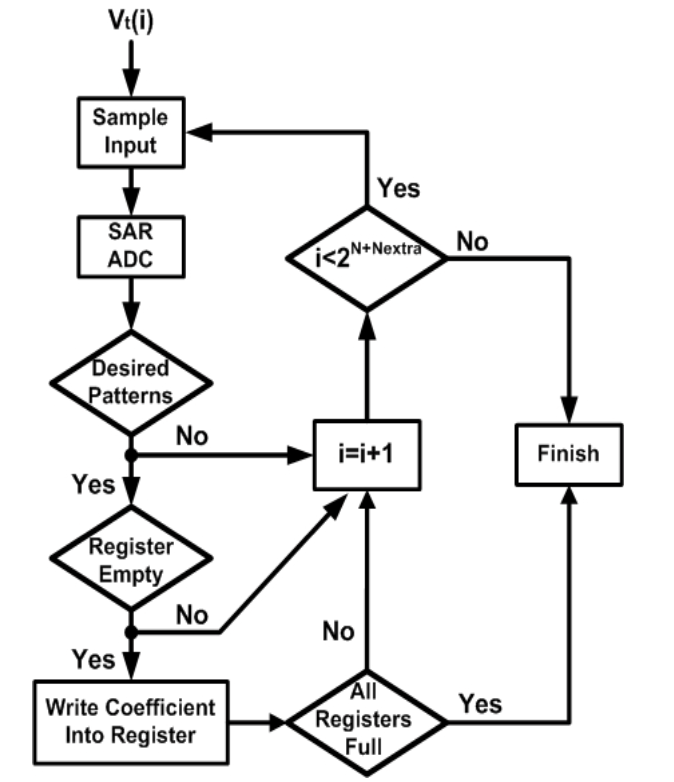

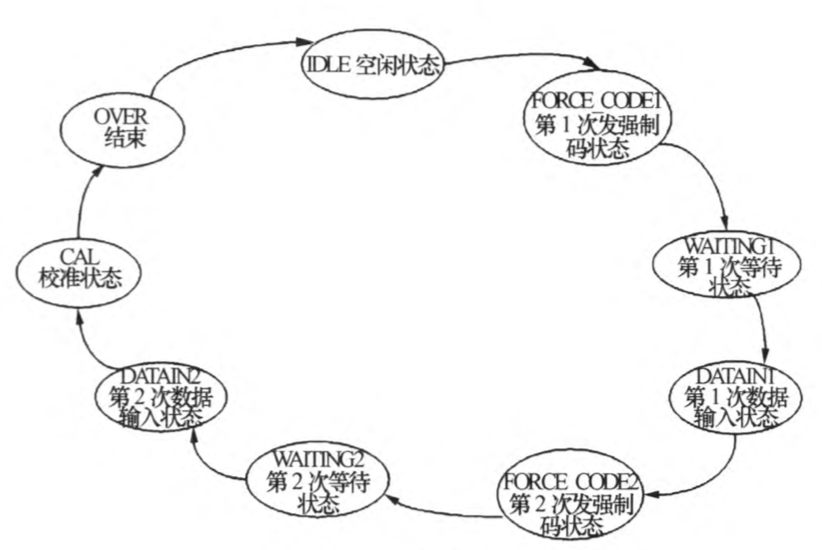

有限状态机

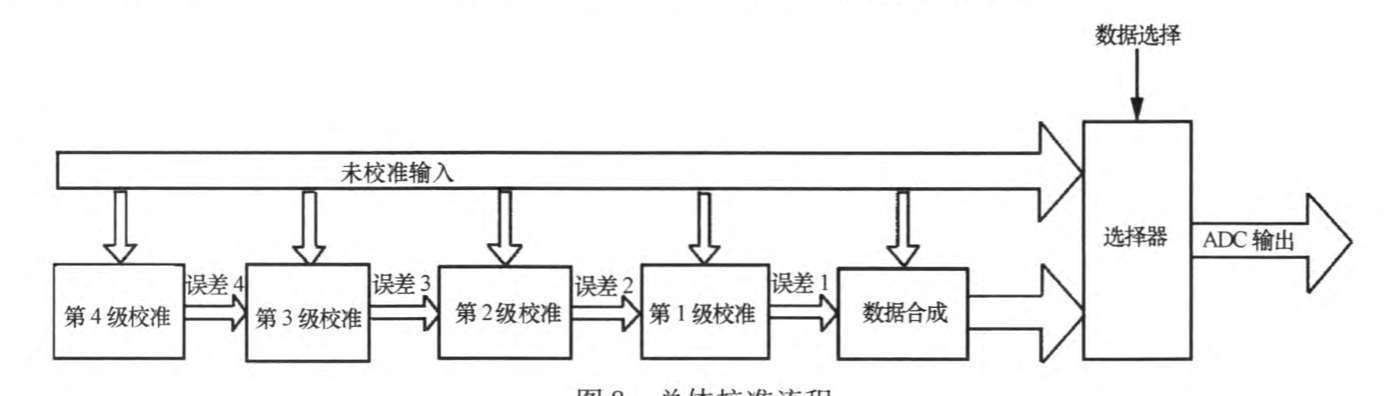

采用有 限状态机的方法一。1刨计算每级校准误差,将每级的校 准信息存入寄存器中。误差运算结束后,将校准参数 对输出码进行校准运算,得到校准后的数字码输出。此数字校准算法可校准对ADC线性影响最大的电容失配误差,适合于1.5 bit级电路和多bit级电 路。明显提高了流水线ADC的无杂散动态范围和有效精度,对模拟电路的改动较小。

-

LMS

-

迭代法

开题 答辩稿

- 各位老师好,我是jll,今天我研究的方向是针对ADC的片上数字校准系统。

Σ-Δ ADC 也可以看作是一个同步电压-频率转换器,后跟一个计数器。如果在足够数量的样本中对输出数据流中“1”的数量进行计数,则计数器输出将表示输入的数字值。

调制器中的积分器表示为模拟低通滤波器,其传递函数等于 H(f) = 1/f。该传递函数具有与输入频率成反比的幅度响应。 1 位量化器生成量化噪声 Q,将其注入输出求和块。如果我们让输入信号为 X,输出 Y,那么从输入加法器出来的信号必须是 X – Y。这乘以滤波器传递函数 1/f,结果进入输出夏天。通过检查,我们可以将输出电压 Y 的表达式写为:

请注意,随着频率 f 接近零,输出电压 Y 接近 X 时没有噪声成分。在较高频率下,信号分量的幅度接近零,噪声分量接近 Q。在高频下,输出主要由量化噪声组成。本质上,模拟滤波器对信号有低通作用,对量化噪声有高通作用。因此,模拟滤波器在 Σ-Δ 调制器模型中执行噪声整形功能。

多级噪声整形 (MASH)

研究方案

-

研究目标

比较现有不同校准算法性能及功耗,针对adc片上校准系统做校准精度、面积、功耗优化

-

研究内容

在20世纪50年代和60年代,直流性能指标(如积分非线性、微分非线性、单调性、无缺失码、增益误差、偏移误差和漂移等)主要用于表征数据转换器。在这个时代,这些规范是足够的,因为大多数早期应用(例如,PCM和雷达除外)处理直流或低频信号,如工业测量和过程控制中遇到的信号。随着20世纪70年代和80年代微处理器和数字信号处理(DSP)的出现,需要动态性能规范,如信噪比(SNR)、无杂散动态范围(SFDR)等,以便充分描述转换器的特性,以用于更复杂的信号处理应用。

现代数据转换器的应用范围包括从低频工业测量到宽带无线电接收机的频谱。尽管直流规范的重要性通常随着信号频率的增加而降低,但在许多应用中它们仍然很重要。例如,中频采样应用中的显著增益和/或偏移误差可导致信号削波,从而降低SNR和SFDR。在需要匹配转换器的应用中,如交织、同步采样和I/Q信号处理,各个转换器之间的相对增益和偏移匹配至关重要。

流水线型ADC、逐次逼近型ADC、 ∑–△ ADC是现在比较常用和符合未来发展需要的ADC类型, 各有其优势和特点,研究其校准系统是保证其基本性能和精度的必然要求。为此,深入去研究对比现有方案,探索更多基准性能的校准系统是研究ADC设备的必然一步。

研究实现现有ADC校准方案,建立统一分析模型,分析其各项性能指标,先做出评测系统,然后针对性的对面积和功耗进行优化,优化现有方案或研究新的方案,争取实现指标突破。

-

拟采取的研究方法及可行性分析

- 阅读相关文献,理解现有校准方案

- 根据调研至少确定五种以上校准方案,在fpga上进行硬件实现

- 比较每种方案优劣,分析其性能功耗面积

- 优化和探索新的实现思路,实现adc校准系统各项指标优化

references

[1]丁洋, 王宗民. 一种基于统计的流水线ADC数字后台校准方法[J]. 微电子学与计算机, 2011, 28(2):5. >>>

[1]郭静宜, 李冬梅, 刘力源,等. 一种适用于流水线ADC的数字校准算法的硬件实现[J]. 高技术通讯, 2009(03):290-294. >>>

[1]吴俊杰, 朱从益, 刘海涛. 一种应用于流水线ADC数字校准算法及实现[J]. 现代雷达, 2014, 36(9):44-48. >>>

[1]戴澜, 周玉梅, 胡晓宇,等. 一种流水线ADC数字校准算法实现[J]. 半导体学报:英文版, 2008, 29(5):5. >>>

[1]张文莲. 折叠内插ADC中数字校准电路设计[J]. 电子制作, 2020(13):4. >>>

[1]杨一波. 时分交替ADC系统数字校准算法与FPGA实现[D]. 电子科技大学. >>>

[1]宫月红, 罗敏, 金杰. 流水线型ADC误差及相应校正策略研究[J]. 微电子学与计算机, 2014(5).

[1]贾英江, 王维斌. ADC综述[J]. 电子测量技术, 1999, 000(004):10-13.

[1] Fukazawa M , Oshima T , Fujiwara M , et al. A CT 2-2 MASH Δ Σ ADC With Multi-Rate LMS-Based Background Calibration and Input-Insensitive Quantization-Error Extraction[J]. IEEE Journal of Solid-State Circuits, 2021, PP(99):1-1. >>>

[1]Moon, Un-Ko, Bang-Sup, et al. Background digital calibration techniques for pipelined ADC's.[J]. IEEE Transactions on Circuits & Systems Part II: Analog & Digital Signal Processing, 1997, 44(2):102-102. >>>

[1] Wei L , Tao W , Temes G C . Digital foreground calibration methods for SAR ADCs[C]// IEEE. IEEE, 2012. >>>

[1]Grace, C. R , Hurst, et al. A 12-bit 80-MSample/s pipelined ADC with bootstrapped digital calibration[J]. Solid-State Circuits, IEEE Journal of, 2005, 40(5):1038-1046. >>>

[1] Lee Z M , Wang C Y , Wu J T . A CMOS 15-bit 125-MS/s Time-Interleaved ADC With Digital Background Calibration[J]. IEEE Journal of Solid-State Circuits, 2007, 42(10):2149-2160. >>>

[1] Shu Y S . Background digital calibration techniques for high-speed, high resolution analog-to-digital data converters[J]. Dissertations & Theses, 2008. >>>

[1] B lecker, E. B , Mcdonald T M , Erdogan O E , et al. Digital Background Calibration of an Algorithmic Analog-to-Digital Converter Using a Simplified Queue[J]. IEEE Journal of Solid-State Circuits, 2003, 38(6):p.1059-1062.

[1] 数据转换器学习与设计

[1] [Time-Interleaved Analog-to-Digital Converters](Time-Interleaved Analog-to-Digital Converters)

-

Taking the Mystery out of the Infamous Formula, "SNR = 6.02N + 1.76dB," and Why You Should Care

-

What the Nyquist Criterion Means to Your Sampled Data System Design

-

Understand SINAD, ENOB, SNR, THD, THD + N, and SFDR so You Don't Get Lost in the Noise Floor

-

The Good, the Bad, and the Ugly Aspects of ADC Input Noise—Is No Noise Good Noise?

-

ADC Noise Figure—An Often Misunderstood and Misinterpreted Specification

-

Aperture Time, Aperture Jitter, Aperture Delay Time— Removing the Confusion

-

The Importance of Data Converter Static Specifications— Don't Lose Sight of the Basics!