完善adc分类

This commit is contained in:

parent

f5f5c16caa

commit

e37c3eb3cd

70

README.md

70

README.md

@ -12,22 +12,32 @@

|

||||

|

||||

- 并行ADC

|

||||

|

||||

并行结构的数据转换器的基本思想是:同时比较待转换的信号电平与所有级别的量化电平之间的关系,在模拟信号和数字信号之间相互转换。并行结构所对应的A/D和D/A转换器件分别为Flash-ADC和串状DAC。

|

||||

并行结构的数据转换器的基本思想是:同时比较待转换的信号电平与所有级别的量化电平之间的关系,在模拟信号和数字信号之间相互转换。并行结构所对应的A/D和D/A转换器件分别为Flash-ADC和串状DAC。

|

||||

|

||||

Flash-ADC内含一列并联比较器,一列由电阻分压器产生的电平作为相应的比较器的基准电压。被转换的模拟电压信号同时加到全部比较器上,各比较器的输出经编码后作为ADC的输出,如图2.12所示。

|

||||

Flash-ADC内含一列并联比较器,一列由电阻分压器产生的电平作为相应的比较器的基准电压。被转换的模拟电压信号同时加到全部比较器上,各比较器的输出经编码后作为ADC的输出,如图2.12所示。

|

||||

|

||||

一个分辨率为N(bit)的Flash-ADC含有2N个精密电阻,2N−1个高速比较器;分辨率每增加1bit,需要增加2N个精密电阻和2N个高速比较器,这会大大增加集成的复杂度和器件功耗。因此一般Flash-ADC的分辨率无法达到很高。

|

||||

一个分辨率为N(bit)的Flash-ADC含有2N个精密电阻,2N−1个高速比较器;分辨率每增加1bit,需要增加2N个精密电阻和2N个高速比较器,这会大大增加集成的复杂度和器件功耗。因此一般Flash-ADC的分辨率无法达到很高。

|

||||

|

||||

串状DAC是实现Flash-ADC的逆操作,因使用电阻串来构造参考电压而得名,在有的书中也被称为开尔文分配器。串状DAC依靠待转换数据来控制一组开关,以产生合适的电流通过精密电阻,从而产生合适的模拟信号电压。

|

||||

串状DAC是实现Flash-ADC的逆操作,因使用电阻串来构造参考电压而得名,在有的书中也被称为开尔文分配器。串状DAC依靠待转换数据来控制一组开关,以产生合适的电流通过精密电阻,从而产生合适的模拟信号电压。

|

||||

|

||||

并行结构只需要一级模拟电路,因此具有设计简单,转换时间短,速度快的优点,在所有可能的结构中提供最快的数据转换。在分辨率要求较低的情况下,Flash-ADC和串状DAC两种结构都容易采用超大规模集成电路(VLSI)进行设计。然而,由于比较器(或开关)和精密电阻的数量随着转换器的分辨率呈指数增长,Flash-ADC和串状DAC的芯片面积和功耗也随之呈指数增长。

|

||||

并行结构只需要一级模拟电路,因此具有设计简单,转换时间短,速度快的优点,在所有可能的结构中提供最快的数据转换。在分辨率要求较低的情况下,Flash-ADC和串状DAC两种结构都容易采用超大规模集成电路(VLSI)进行设计。然而,由于比较器(或开关)和精密电阻的数量随着转换器的分辨率呈指数增长,Flash-ADC和串状DAC的芯片面积和功耗也随之呈指数增长。

|

||||

|

||||

- 流水线型ADC

|

||||

|

||||

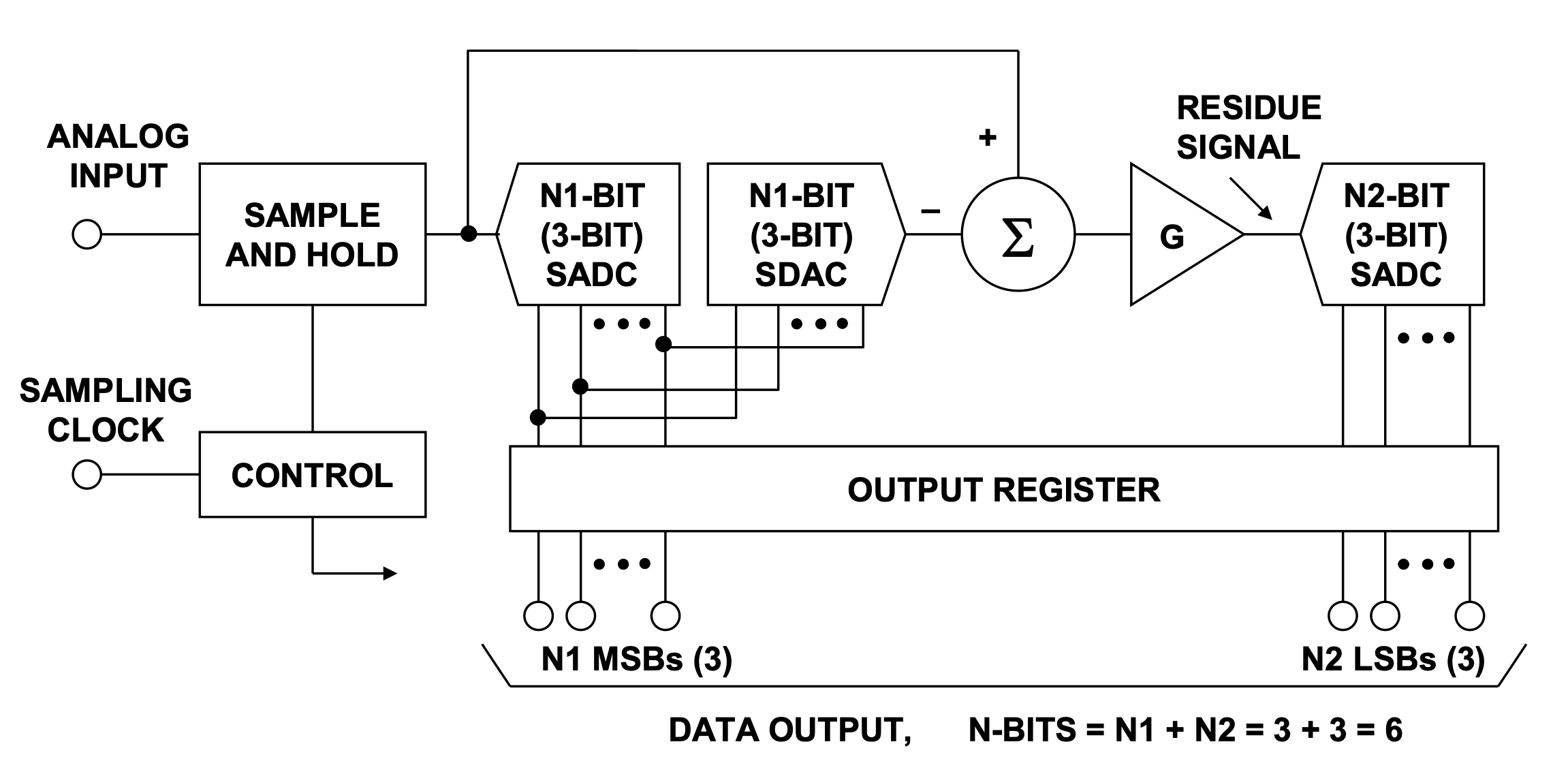

在采样率于5msps到10msps之间的应用中,流水线ADC体系结构占主导地位。尽管在20世纪80年代和90年代初,全并行体系结构主导了8 bit video IC ADC市场,但流水线体系结构在现代应用中已基本上取代了闪存ADC。有少量采样率大于1GHz的高功率砷化镓(GaAs)闪存转换器,但分辨率限于6或8位。然而,flash转换器仍然是高分辨率流水线ADC的一个流行构件。

|

||||

|

||||

流水线ADC的应用包括视频、图像处理、通信等方面。该体系结构适用于各种成本相对较低的IC工艺,如CMOS和BiCMOS。目前的技术在采样率大于100msps时能达到12到16位的分辨率。

|

||||

|

||||

|

||||

|

||||

流水线 ADC 通常由 N 个位数相同或不相同的 低分辨率子级组成 ,除最后一级外 ,每个子级都包括 子 ADC 、子 DAC 、减法电路和余量放大器 ,其中子 DAC 、减法电路和余量放大器组合在一起称为 MDAC .

|

||||

|

||||

- 逐次逼近型ADC(SAR)

|

||||

|

||||

多年来,SAR ADC一直是数据采集系统的主流。最近的设计改进将这些ADC的采样频率扩展到兆赫范围,分辨率为18位。模拟设备PulSAR®系列SAR ADC使用内部开关电容技术和自动校准,并在CMOS工艺上以2 MSPS(AD7641)提供18位,无需昂贵的薄膜激光微调。在16位级别,AD7625(6 MSPS)和AD7626(10 MSPS)也代表了突破性的技术。

|

||||

|

||||

|

||||

|

||||

SAR ADC 分多步执行转换, 转换步骤数等 于ADC转换器中的位数。每个步骤均由ADC时钟驱动。每个ADC时钟从结果到输出产生一 位。ADC的内部设计基于切换电容技术。

|

||||

|

||||

以10bit ADC为例

|

||||

@ -40,7 +50,29 @@

|

||||

|

||||

- ∑–△ ADC

|

||||

|

||||

-

|

||||

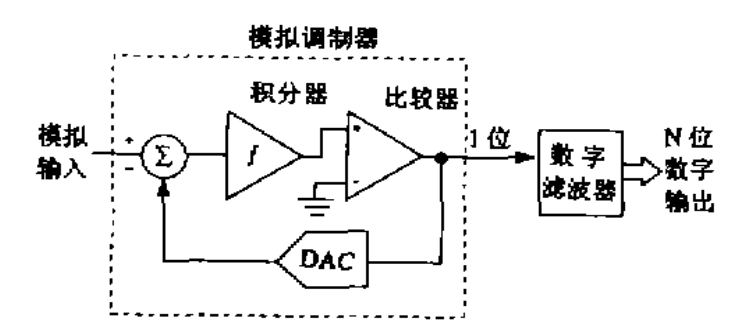

sigma-delta ADC是现代声带、音频和高分辨率精密工业测量应用的首选转换器。高度数字化的体系结构非常适合现代fine-line CMOS工艺,因此可以在不显著增加成本的情况下轻松添加数字功能。由于它的广泛使用,了解这种转换器架构背后的基本原理非常重要。

|

||||

|

||||

|

||||

|

||||

|

||||

|

||||

这种ADC又称为过采样转换器,其结构较简单。它由∑–△调制器及连接于其后的数字滤故器构成。调制器的结构近似于双斜率ADC,包括一个积分器和一个比较器,以及含有一个1位DAC的反馈环。这个内置的DAC仅仅是一个开关。它将积分器输入切换到一个正或负的参考电压。∑–△ADC还包括一个时钟单元.为调制器和数字滤波器提供适当的定时。窄带信号送人∑–△ADC后以非常低的分辨率(1位)进行量化,但采样频率却非常高.如2MHz或更高。经过数字滤波处理后 .这种过采样速率被降低到8kHz左右,同时ADC的分辨率(即动态范围 ) 被提高到16位或更高。尽管比流水线ADC慢且输入带宽较窄,∑–△ADC仍具有以下三种优势:

|

||||

|

||||

- 低价格、高性能

|

||||

- 集成化的数字滤波

|

||||

- 与DSP技术兼容,便于实现系统集成

|

||||

|

||||

- 积分型ADC

|

||||

|

||||

|

||||

|

||||

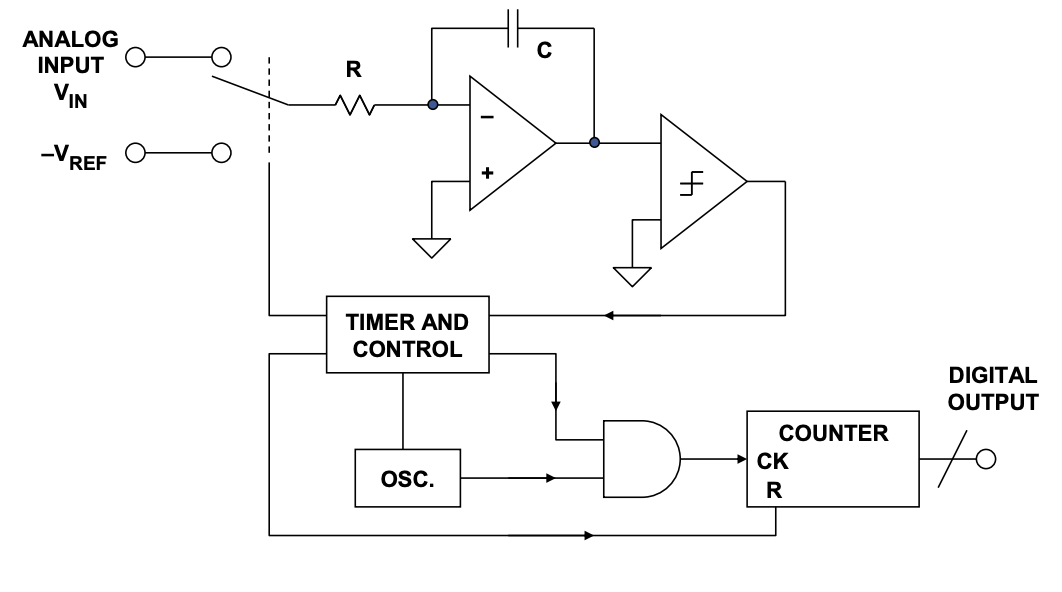

积分型ADC又称双斜率或多斜率数据转换器,是应用最为广泛的转换器类型。经典的双斜率转换器包括两个主要部分:一部分电路采样并量化输入电压.产生一个时域间隔或脉冲序列;再由一个计数器将其转换为数字量输出。双斜率转换器采用一个带有输入切换开头关的模拟积分器,一个比较器和一个计数单元。积分器对输入电压积分固定的时间间隔Tm幢,诙时间间隔通常对应于内部计数单元的最大计数(如图4所示)时间到达后将计数器复位井将积分器输入连接到反极性(负)参考电压。在这个反扳性信号作用下积分器被“反向积分直到括出回到零,井使计数器终止 ,积分器复位。

|

||||

|

||||

- 折叠型ADC (Folding ADC)

|

||||

|

||||

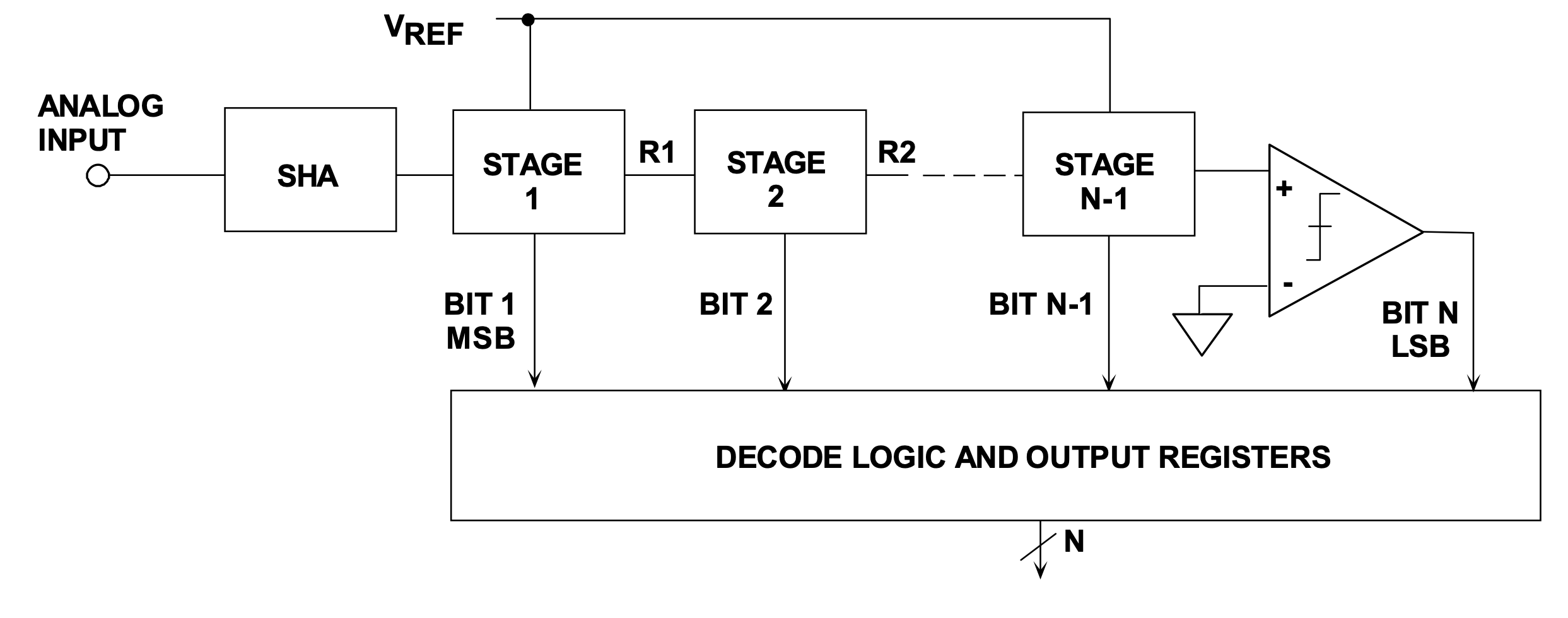

“折叠”架构使用每比特一级执行A/D转换,总体概念如图1所示。每级一位且无纠错的多级流水线ADC基本上是bit-per-stage转换器。实际上,这种类型的流水线转换器通常使用每级1.5bit的方法来提供错误校正。

|

||||

|

||||

|

||||

|

||||

#### ADC误差分析

|

||||

|

||||

@ -118,6 +150,8 @@

|

||||

|

||||

|

||||

|

||||

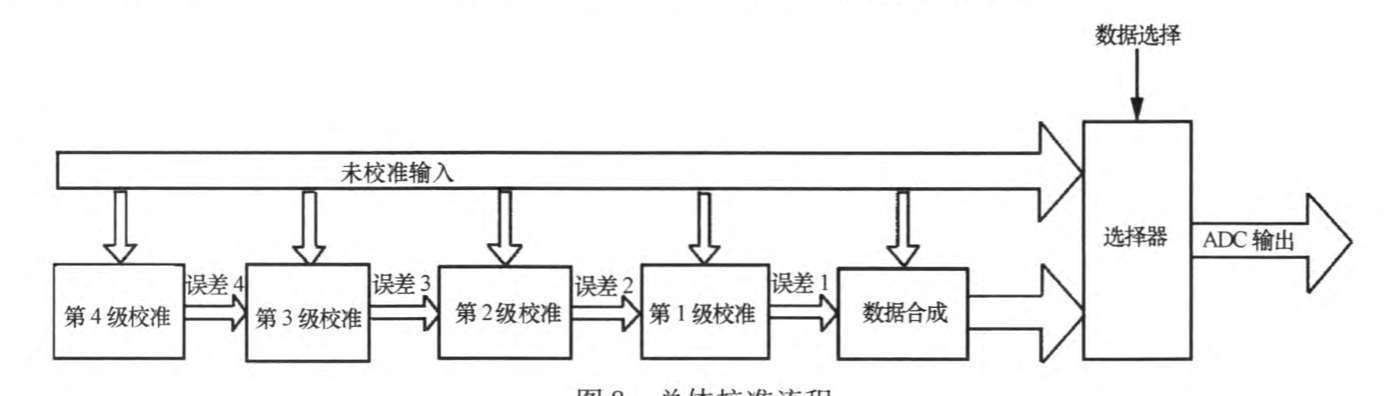

采用有 限状态机的方法一。1刨计算每级校准误差,将每级的校 准信息存入寄存器中。误差运算结束后,将校准参数 对输出码进行校准运算,得到校准后的数字码输出。此数字校准算法可校准对ADC线性影响最大的电容失配误差,适合于1.5 bit级电路和多bit级电 路。明显提高了流水线ADC的无杂散动态范围和有 效精度,对模拟电路的改动较小。

|

||||

|

||||

- LMS

|

||||

|

||||

- 迭代法

|

||||

@ -128,16 +162,21 @@

|

||||

|

||||

1. 研究目标

|

||||

|

||||

比较现有不同校准算法性能及功耗,针对片上系统adc做优化控制面积和功耗

|

||||

比较现有不同校准算法性能及功耗,针对adc片上校准系统做面积和功耗优化

|

||||

|

||||

2. 研究内容

|

||||

|

||||

|

||||

流水线型ADC 逐次逼近型ADC ∑–△ ADC是现在比较常用和符合未来发展需要的ADC类型, 各有其优势和特点,实现

|

||||

|

||||

3. 拟解决的问题

|

||||

|

||||

4. 拟采取的研究方法及可行性分析

|

||||

|

||||

- 阅读相关文献,理解现有校准方案

|

||||

- 根据调研至少确定五种以上校准方案,在fpga上进行硬件实现

|

||||

- 比较每种方案优劣,分析其性能功耗面积

|

||||

- 优化和探索新的实现思路,实现adc校准系统各项指标优化

|

||||

|

||||

|

||||

|

||||

### references

|

||||

@ -156,6 +195,8 @@

|

||||

|

||||

[1]宫月红, 罗敏, 金杰. 流水线型ADC误差及相应校正策略研究[J]. 微电子学与计算机, 2014(5).

|

||||

|

||||

[1]贾英江, 王维斌. ADC综述[J]. 电子测量技术, 1999, 000(004):10-13.

|

||||

|

||||

[1] Fukazawa M , Oshima T , Fujiwara M , et al. A CT 2-2 MASH Δ Σ ADC With Multi-Rate LMS-Based Background Calibration and Input-Insensitive Quantization-Error Extraction[J]. IEEE Journal of Solid-State Circuits, 2021, PP(99):1-1. [>>>](https://public.veypi.com/research/digitalcalibration/citations/A%20CT%202-2%20MASH%20--%20ADC%20With%20Multi-Rate%20LMS-Based%20Background%20Calibration%20and%20Input-Insensitive%20Quantization-Error%20Extraction.pdf)

|

||||

|

||||

[1]Moon, Un-Ko, Bang-Sup, et al. Background digital calibration techniques for pipelined ADC's.[J]. IEEE Transactions on Circuits & Systems Part II: Analog & Digital Signal Processing, 1997, 44(2):102-102. [>>>](https://public.veypi.com/research/digitalcalibration/citations/Background%20Digital%20Calibration%20Techniques%20for%20Pipelined%20ADC%E2%80%99s.pdf)

|

||||

@ -175,3 +216,16 @@

|

||||

- [sar adc](https://www.cnblogs.com/nevel/p/6151671.html)

|

||||

- [adc category](https://blog.csdn.net/ZQ07506149/article/details/82557492)

|

||||

- [adc error](https://www.21ic.com/article/849518.html)

|

||||

- [∑–△](https://www.cnblogs.com/nevel/p/6152340.html)

|

||||

|

||||

- [Taking the Mystery out of the Infamous Formula, "SNR = 6.02N + 1.76dB," and Why You Should Care](https://www.analog.com/media/en/training-seminars/tutorials/MT-001.pdf)

|

||||

- [What the Nyquist Criterion Means to Your Sampled Data System Design ](https://www.analog.com/media/en/training-seminars/tutorials/MT-002.pdf)

|

||||

- [Understand SINAD, ENOB, SNR, THD, THD + N, and SFDR so You Don't Get Lost in the Noise Floor ](https://www.analog.com/media/en/training-seminars/tutorials/MT-003.pdf)

|

||||

- [The Good, the Bad, and the Ugly Aspects of ADC Input Noise—Is No Noise Good Noise? ](https://www.analog.com/media/en/training-seminars/tutorials/MT-004.pdf)

|

||||

- [Noise Power Ratio (NPR)—A 65-Year Old Telephone System Specification Finds New Life in Modern Wireless Applications](https://www.analog.com/media/en/training-seminars/tutorials/MT-005.pdf)

|

||||

- [ADC Noise Figure—An Often Misunderstood and Misinterpreted Specification](https://www.analog.com/media/en/training-seminars/tutorials/MT-006.pdf)

|

||||

- [Aperture Time, Aperture Jitter, Aperture Delay Time— Removing the Confusion](https://www.analog.com/media/en/training-seminars/tutorials/MT-007.pdf)

|

||||

- [Converting Oscillator Phase Noise to Time Jitter](https://www.analog.com/media/en/training-seminars/tutorials/MT-008.pdf)

|

||||

- [Data Converter Codes—Can You Decode Them?](https://www.analog.com/media/en/training-seminars/tutorials/MT-009.pdf)

|

||||

- [The Importance of Data Converter Static Specifications— Don't Lose Sight of the Basics!](https://www.analog.com/media/en/training-seminars/tutorials/MT-010.pdf)

|

||||

- [Find Those Elusive ADC Sparkle Codes and Metastable States ](https://www.analog.com/media/en/training-seminars/tutorials/MT-011.pdf)

|

||||

|

||||

35

references.md

Normal file

35

references.md

Normal file

@ -0,0 +1,35 @@

|

||||

# references

|

||||

|

||||

|

||||

|

||||

- [Taking the Mystery out of the Infamous Formula, "SNR = 6.02N + 1.76dB," and Why You Should Care](https://www.analog.com/media/en/training-seminars/tutorials/MT-001.pdf)

|

||||

- [What the Nyquist Criterion Means to Your Sampled Data System Design ](https://www.analog.com/media/en/training-seminars/tutorials/MT-002.pdf)

|

||||

- [Understand SINAD, ENOB, SNR, THD, THD + N, and SFDR so You Don't Get Lost in the Noise Floor ](https://www.analog.com/media/en/training-seminars/tutorials/MT-003.pdf)

|

||||

- [The Good, the Bad, and the Ugly Aspects of ADC Input Noise—Is No Noise Good Noise? ](https://www.analog.com/media/en/training-seminars/tutorials/MT-004.pdf)

|

||||

- [Noise Power Ratio (NPR)—A 65-Year Old Telephone System Specification Finds New Life in Modern Wireless Applications](https://www.analog.com/media/en/training-seminars/tutorials/MT-005.pdf)

|

||||

- [ADC Noise Figure—An Often Misunderstood and Misinterpreted Specification](https://www.analog.com/media/en/training-seminars/tutorials/MT-006.pdf)

|

||||

- [Aperture Time, Aperture Jitter, Aperture Delay Time— Removing the Confusion](https://www.analog.com/media/en/training-seminars/tutorials/MT-007.pdf)

|

||||

- [Converting Oscillator Phase Noise to Time Jitter](https://www.analog.com/media/en/training-seminars/tutorials/MT-008.pdf)

|

||||

- [Data Converter Codes—Can You Decode Them?](https://www.analog.com/media/en/training-seminars/tutorials/MT-009.pdf)

|

||||

- [The Importance of Data Converter Static Specifications— Don't Lose Sight of the Basics!](https://www.analog.com/media/en/training-seminars/tutorials/MT-010.pdf)

|

||||

- [Find Those Elusive ADC Sparkle Codes and Metastable States ](https://www.analog.com/media/en/training-seminars/tutorials/MT-011.pdf)

|

||||

- [Intermodulation Distortion Considerations for ADCs ](https://www.analog.com/media/en/training-seminars/tutorials/MT-012.pdf)

|

||||

- [Evaluating High Speed DAC Performance ](https://www.analog.com/media/en/training-seminars/tutorials/MT-013.pdf)

|

||||

- [Basic DAC Architectures I: String DACs and Thermometer (Fully Decoded) DACs ](https://www.analog.com/media/en/training-seminars/tutorials/MT-014.pdf)

|

||||

- [Basic DAC Architectures II: Binary DACs](https://www.analog.com/media/en/training-seminars/tutorials/MT-015.pdf)

|

||||

- [Basic DAC Architectures III: Segmented DACs](https://www.analog.com/media/en/training-seminars/tutorials/MT-016.pdf)

|

||||

- [Oversampling Interpolating](https://www.analog.com/media/en/training-seminars/tutorials/MT-017.pdf)

|

||||

- [Intentionally Nonlinear DACs](https://www.analog.com/media/en/training-seminars/tutorials/MT-018.pdf)

|

||||

- [DAC Interface Fundamentals ](https://www.analog.com/media/en/training-seminars/tutorials/MT-019.pdf)

|

||||

- [ADC Architectures I: The Flash Converter](https://www.analog.com/media/en/training-seminars/tutorials/MT-020.pdf)

|

||||

- [ADC Architectures II: Successive Approximation ADCs ](https://www.analog.com/media/en/training-seminars/tutorials/MT-021.pdf)

|

||||

- [ADC Architectures III: Sigma-Delta ADC Basics ](https://www.analog.com/media/en/training-seminars/tutorials/MT-022.pdf)

|

||||

- [ADC Architectures IV: Sigma-Delta ADC Advanced Concepts and Applications ](https://www.analog.com/media/en/training-seminars/tutorials/MT-023.pdf)

|

||||

- [ADC Architectures V: Pipelined Subranging ADCs](https://www.analog.com/media/en/training-seminars/tutorials/MT-024.pdf)

|

||||

- [ADC Architectures VI: Folding ADCs ](https://www.analog.com/media/en/training-seminars/tutorials/MT-025.pdf)

|

||||

- [ADC Architectures VII: Counting ADCs](https://www.analog.com/media/en/training-seminars/tutorials/MT-026.pdf)

|

||||

- [ADC Architectures VIII: Integrating ADCs ](https://www.analog.com/media/en/training-seminars/tutorials/MT-027.pdf)

|

||||

- [Voltage-to-Frequency Converters](https://www.analog.com/media/en/training-seminars/tutorials/MT-028.pdf)

|

||||

- [Optical Encoders ](https://www.analog.com/media/en/training-seminars/tutorials/MT-029.pdf)

|

||||

- [Resolver-to-Digital Converters](https://www.analog.com/media/en/training-seminars/tutorials/MT-030.pdf)

|

||||

- [Grounding Data Converters and Solving the Mystery of "AGND" and "DGND" ](https://www.analog.com/media/en/training-seminars/tutorials/MT-031.pdf)

|

||||

Loading…

x

Reference in New Issue

Block a user