针对adc的片上数字校准系统研究

[TOC]

研究意义

模数转换器是各种数字系统中不可缺少的组成部分,其性能的优劣直接关系整体系统的性能和功能发挥,随着处理器和信号处理技术的不断发展,对adc的性能要求也越来越高,高速高精度已成为信号处理领域必要要求。但是,随着流水线ADC的精度提高的12bit以上时,工艺的偏差导致的电容失配、运放的非理想性等误差使得ADC的精度收到了限制,通过传统模拟电路的设计方法已无法设计出符合要求的高精高速ADC。为实现ADC的高精度,采用数字校准的方法对采集的数据进行误差校准,由于其鲁棒性、灵活性且不打断AD转换,可以有效补偿工艺偏差带来的系统误差,提高流水线ADC的性能。

研究现状分析

ADC 分类

-

并行ADC

并行结构的数据转换器的基本思想是:同时比较待转换的信号电平与所有级别的量化电平之间的关系,在模拟信号和数字信号之间相互转换。并行结构所对应的A/D和D/A转换器件分别为Flash-ADC和串状DAC。

Flash-ADC内含一列并联比较器,一列由电阻分压器产生的电平作为相应的比较器的基准电压。被转换的模拟电压信号同时加到全部比较器上,各比较器的输出经编码后作为ADC的输出,如图2.12所示。

一个分辨率为N(bit)的Flash-ADC含有2N个精密电阻,2N−1个高速比较器;分辨率每增加1bit,需要增加2N个精密电阻和2N个高速比较器,这会大大增加集成的复杂度和器件功耗。因此一般Flash-ADC的分辨率无法达到很高。

串状DAC是实现Flash-ADC的逆操作,因使用电阻串来构造参考电压而得名,在有的书中也被称为开尔文分配器。串状DAC依靠待转换数据来控制一组开关,以产生合适的电流通过精密电阻,从而产生合适的模拟信号电压。

并行结构只需要一级模拟电路,因此具有设计简单,转换时间短,速度快的优点,在所有可能的结构中提供最快的数据转换。在分辨率要求较低的情况下,Flash-ADC和串状DAC两种结构都容易采用超大规模集成电路(VLSI)进行设计。然而,由于比较器(或开关)和精密电阻的数量随着转换器的分辨率呈指数增长,Flash-ADC和串状DAC的芯片面积和功耗也随之呈指数增长。

-

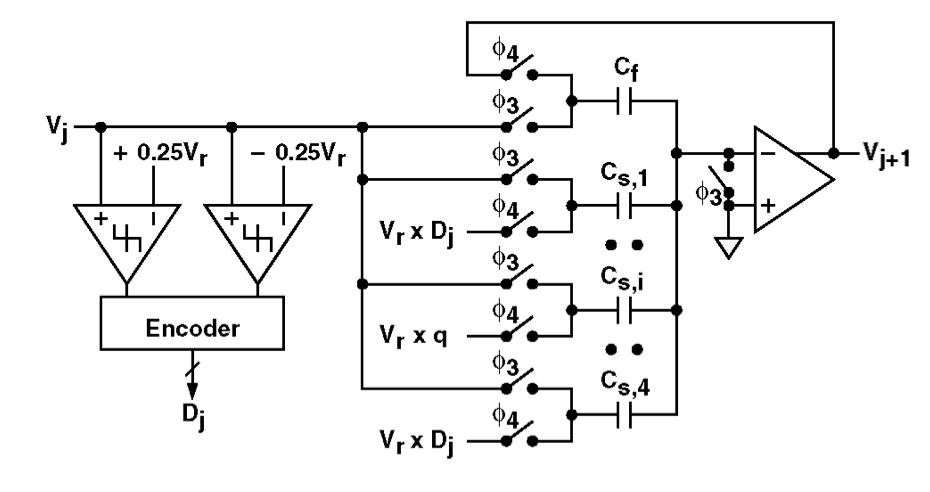

流水线型ADC

流水线 ADC 通常由 N 个位数相同或不相同的 低分辨率子级组成 ,除最后一级外 ,每个子级都包括 子 ADC 、子 DAC 、减法电路和余量放大器 ,其中子 DAC 、减法电路和余量放大器组合在一起称为 MDAC .

-

逐次逼近型ADC(SAR)

SAR ADC 分多步执行转换, 转换步骤数等 于ADC转换器中的位数。每个步骤均由ADC时钟驱动。每个ADC时钟从结果到输出产生一 位。ADC的内部设计基于切换电容技术。

以10bit ADC为例

- 采样状态:电容充电至电压VIN。Sa切换至VIN,采样期间Sb开关闭合

- 保持状态:输入断开,电容保持输入电压。Sb开关打开,然后S1-S11切换至接地且Sa切换至VREF。

- 逐次逼近:第一个逼近步骤。S1切换至VREF。VIN与VREF/2比较。如果MSB = 0,则与¼VREF进行比较,S1切换回接地。S2切换至VREF。如果MSB = 1,则与¾VREF进行比较,S1保持接地。S2切换至VREF。重复如上步骤,直到LSB为止。可以简单理解为二分法逐次进行输入电压与参考电压的比较。首次于VREF/2比较,下次比较根据上次比较结果决定,如果MSB=1则与¾VREF比较。如果MSB=0则与¼VREF比较。后面决定与1/8VREF 3/8VREF、 5/8VREF、 7/8VREF之一做比较。循环直到输出LSB为止。

-

∑–△ ADC

ADC误差分析

要研究ADC数字校准系统,就先要对校准目标有个清晰的认识,明白其误差产生原理,才能针对性去校准误差。 ADC误差主要来源于内部自身转换产生的误差和外部环境造成的误差。

先简单分析下外部环境误差,外部环境并非在生产和研发阶段可以控制的因素,因此也不在片上校准系统校准范围内, 如参考电压噪声、模拟输入信号噪声、ADC动态范围匹配不佳、模拟信号源电阻、注入电流、温度等影响都会对最后转换精度造成影响。

-

量化误差

量化误差是基本误差,用简单3bit ADC来说明。输入电压被数字化,以8个离散电平来划分,分别由代码000b到111b去代表它们,每一代码跨越Vref/8的电压范围。代码大小一般被定义为一个最低有效位(Least Significant Bit,LSB)。若假定Vref=8V时,每个代码之间的电压变换就代表1V。换言之,产生指定代码的实际电压与代表该码的电压两者之间存在误差。一般来说,0.5LSB偏移加入到输入端便导致在理想过渡点上有正负0.5LSB的量化误差。

-

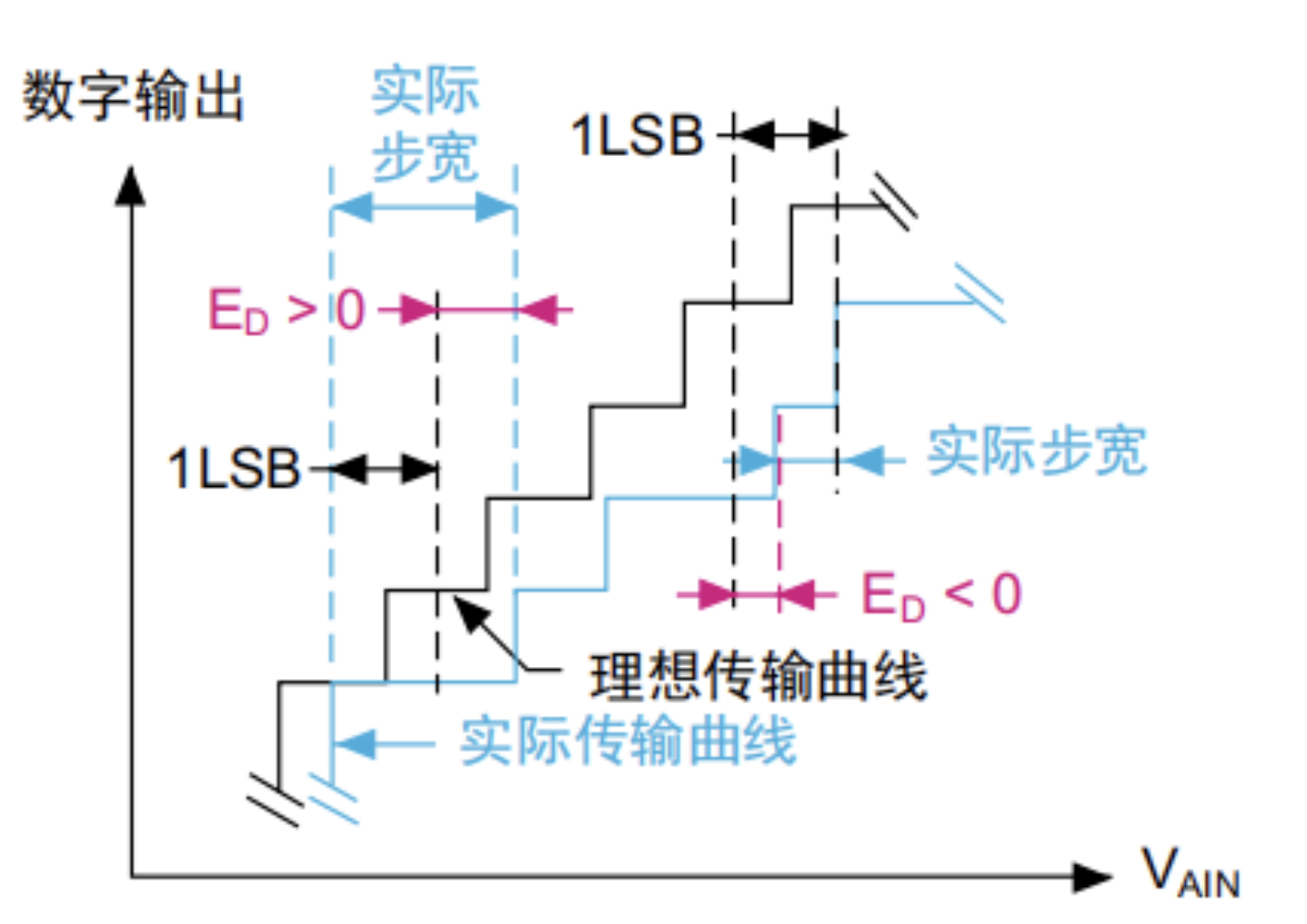

微分非线性误差

微分线性误差(DLE)为实际步进和理想步进之间的最大偏离。这里的“理想情况”不是指理想传输曲线,而是指ADC分辨率。在下图中,用ED表示DLE。

ED = 实际步宽 – 1 LSB

理想情况下,1 LSB的模拟输入电压变化量应导致数字代码变化。如果需要大于1 LSB的模拟输入电压才能导致数字代码变化,将观察到微分线性误差。因此,DLE对应于从一个数字代 码变为下一个数字代码所需的最大额外电压。DLE也称为微分非线性(DLE)误差。

-

积分非线性误差

积分线性误差为任何实际转换和端点相关线间的最大偏离。在下图中,用EL表示ILE。端点相关线可以定义为A/D传输曲线上连接第一次实际转换与最后一次实际转换的线。EL是指与每一次转换的这条线的偏离。因此,端点相关线对应于实际传输曲线并且与理想传输曲线不相关。ILE也称为积分非线性(INL)误差。ILE是整个范围内DLE的积分。

-

增益与偏移误差

偏移误差是第一次实际转换和第一次理想转换之间的偏离。第一次转换发生在数字ADC输出 从0变为1时。理想情况下,当模拟输入介于0.5 LSB和1.5 LSB之间时,数字输出应为1。仍然是理想情况下,第一次转换发生在0.5 LSB处。用EO表示偏移误差。

增益误差是最后一次实际转换和最后一次理想转换之间的偏离。增益误差用EG表示。最后一次实际转换是从0xFFE到0xFFF的转换。理想情况下,当模拟输入等于VREF+ – 0.5 LSB时,应存在从0xFFE到0xFFF的转换。因此对于VREF+= 3.3 V,最后一次理想转换应发生 在3.299597 V处。如果ADC提供VAIN < VREF+ – 0.5 LSB的0xFFF读数,将获得负增益误差。

ADC 校准方案

校准系统分类

-

模拟校准

使用电路补偿器件误差

-

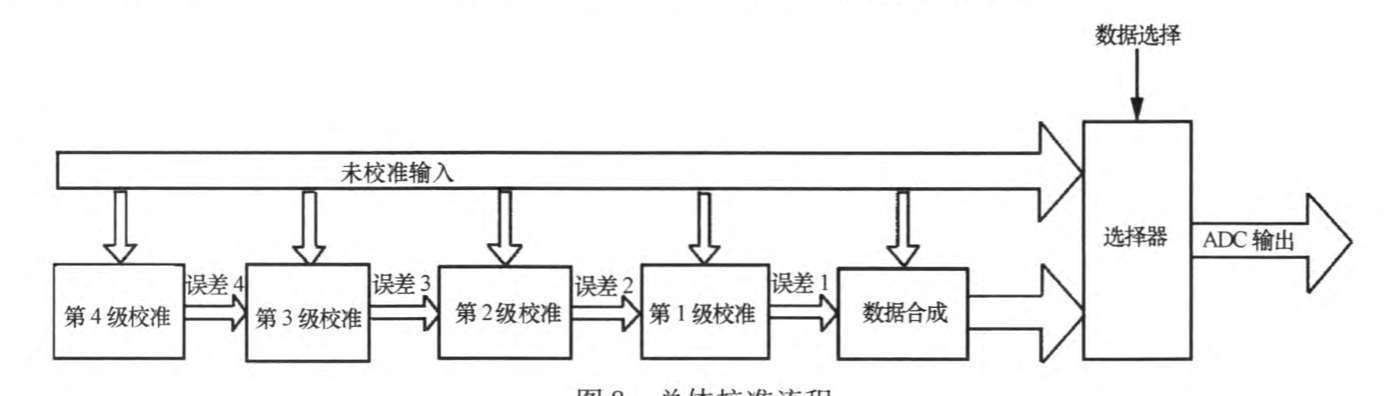

数字校准

-

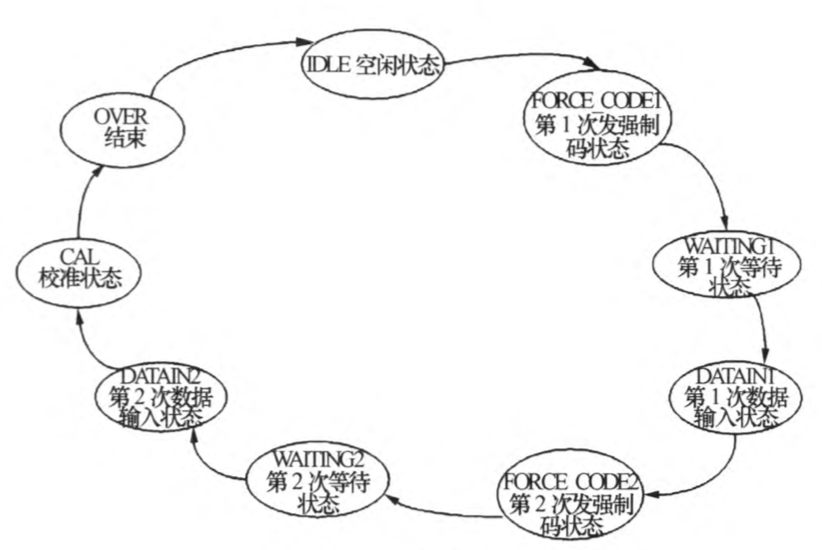

前台校准

校准时ADC不工作, 结束后切换

-

后台校准

ADC工作同时进行误差校准

-

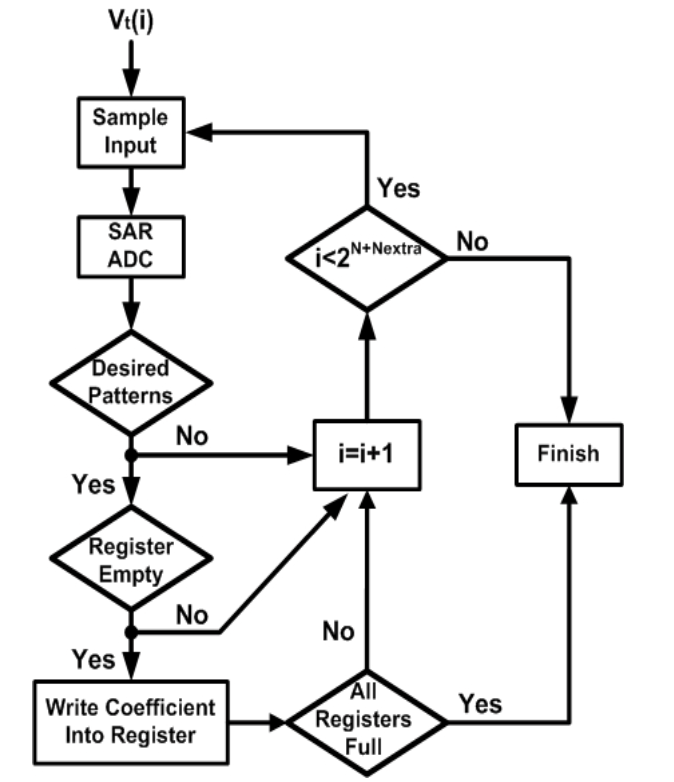

现有校准方法

研究方案

-

研究目标

比较现有不同校准算法性能及功耗,针对片上系统adc做优化控制面积和功耗

-

研究内容

-

拟解决的问题

-

拟采取的研究方法及可行性分析

references

[1]丁洋, 王宗民. 一种基于统计的流水线ADC数字后台校准方法[J]. 微电子学与计算机, 2011, 28(2):5. >>>

[1]郭静宜, 李冬梅, 刘力源,等. 一种适用于流水线ADC的数字校准算法的硬件实现[J]. 高技术通讯, 2009(03):290-294. >>>

[1]吴俊杰, 朱从益, 刘海涛. 一种应用于流水线ADC数字校准算法及实现[J]. 现代雷达, 2014, 36(9):44-48. >>>

[1]戴澜, 周玉梅, 胡晓宇,等. 一种流水线ADC数字校准算法实现[J]. 半导体学报:英文版, 2008, 29(5):5. >>>

[1]张文莲. 折叠内插ADC中数字校准电路设计[J]. 电子制作, 2020(13):4. >>>

[1]杨一波. 时分交替ADC系统数字校准算法与FPGA实现[D]. 电子科技大学. >>>

[1]宫月红, 罗敏, 金杰. 流水线型ADC误差及相应校正策略研究[J]. 微电子学与计算机, 2014(5).

[1] Fukazawa M , Oshima T , Fujiwara M , et al. A CT 2-2 MASH Δ Σ ADC With Multi-Rate LMS-Based Background Calibration and Input-Insensitive Quantization-Error Extraction[J]. IEEE Journal of Solid-State Circuits, 2021, PP(99):1-1. >>>

[1]Moon, Un-Ko, Bang-Sup, et al. Background digital calibration techniques for pipelined ADC's.[J]. IEEE Transactions on Circuits & Systems Part II: Analog & Digital Signal Processing, 1997, 44(2):102-102. >>>

[1] Wei L , Tao W , Temes G C . Digital foreground calibration methods for SAR ADCs[C]// IEEE. IEEE, 2012. >>>

[1]Grace, C. R , Hurst, et al. A 12-bit 80-MSample/s pipelined ADC with bootstrapped digital calibration[J]. Solid-State Circuits, IEEE Journal of, 2005, 40(5):1038-1046. >>>

[1] Lee Z M , Wang C Y , Wu J T . A CMOS 15-bit 125-MS/s Time-Interleaved ADC With Digital Background Calibration[J]. IEEE Journal of Solid-State Circuits, 2007, 42(10):2149-2160. >>>

[1] Shu Y S . Background digital calibration techniques for high-speed, high resolution analog-to-digital data converters[J]. Dissertations & Theses, 2008. >>>

[1] 数据转换器学习与设计

[1] [Time-Interleaved Analog-to-Digital Converters](Time-Interleaved Analog-to-Digital Converters)